System-on-Chip (PSoC) Lab Tapeout Project

Previously, RTL designs were only emulated on FPGA platforms and the ASIC parts of the lab have been limited to simulation. This project extends the existing PSoC teaching materials and RTL base to support full ASIC tapeout, allowing students to experience the complete development flow — from frontend RTL to physical design and final tapeout. It also establishes a foundation for future tapeouts of student designs.

Sign up for the PSoC course here.

The SoC

The SoC is based on the open-source NEORV32 RISC-V core and the NEOSD SD card controller. All components are open source, including RTL, bootloader, firmware, and PCBs.

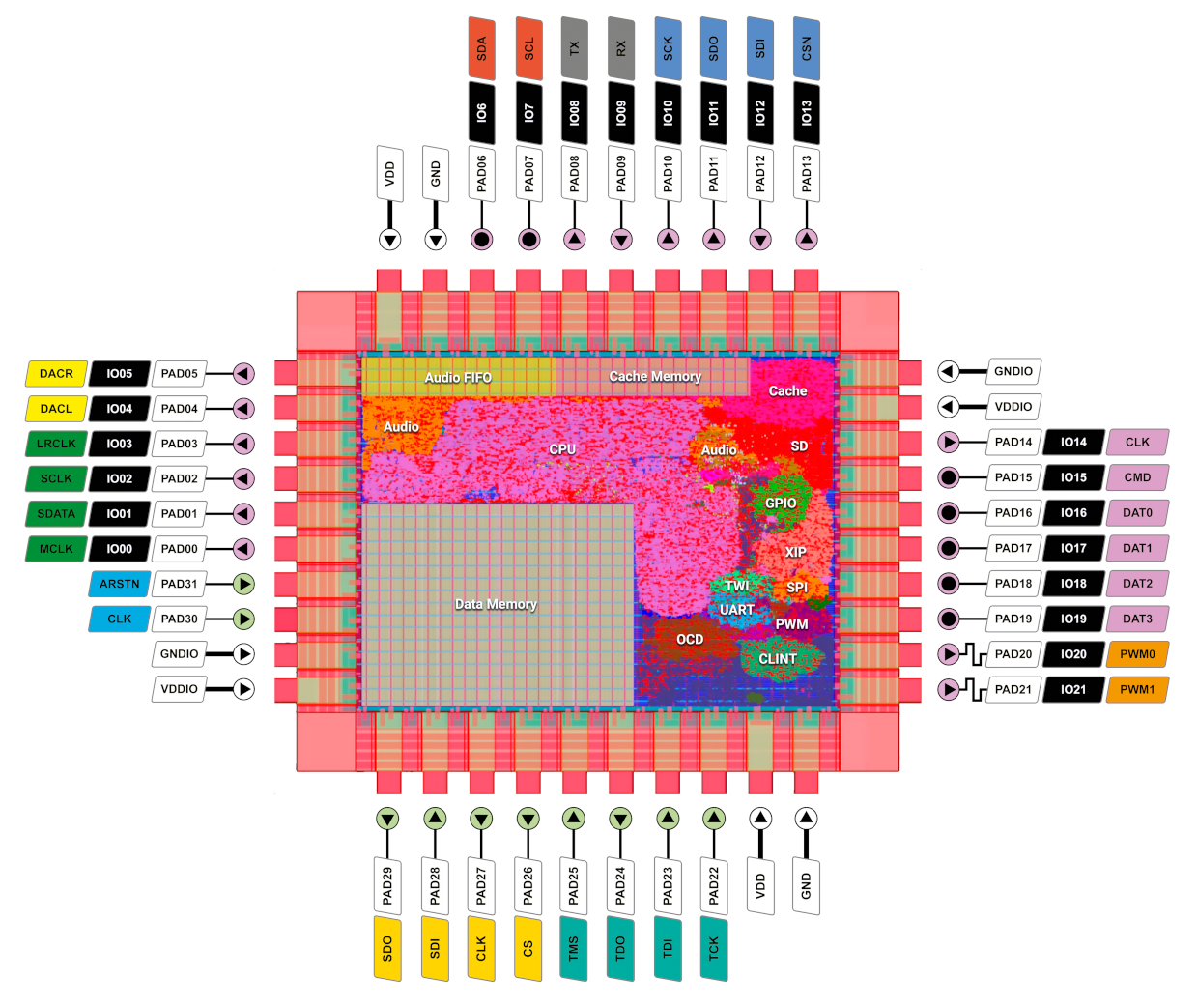

The chip was submitted for fabrication using IHP’s SG13G2 130nm SiGe BiCMOS technology, with dimensions of 2.046 mm × 1.67 mm (3.42 mm² total area). It features 40 pins, 8 of which are power pins.

Supported peripherals include:

- I2S (custom peripheral)

- Delta-Sigma Modulator for Audio (custom peripheral to be designed by students)

- I2C

- UART

- SPI

- SD Card Interface

- PWM

- JTAG for on-chip debugging and programming

- SPI-Flash with execute-in-place support

- GPIO with configurable interrupts

- Instruction cache

- Timer and software interrupts

- Data memory

21 pins can be configured either for their primary function or as GPIO. All GPIOs are configurable as input or output. The SoC requires two supply voltages: 3.3V for I/O and 1.2V for the core. More information is available at https://github.com/kit-kch/psoc-soc.

The Application

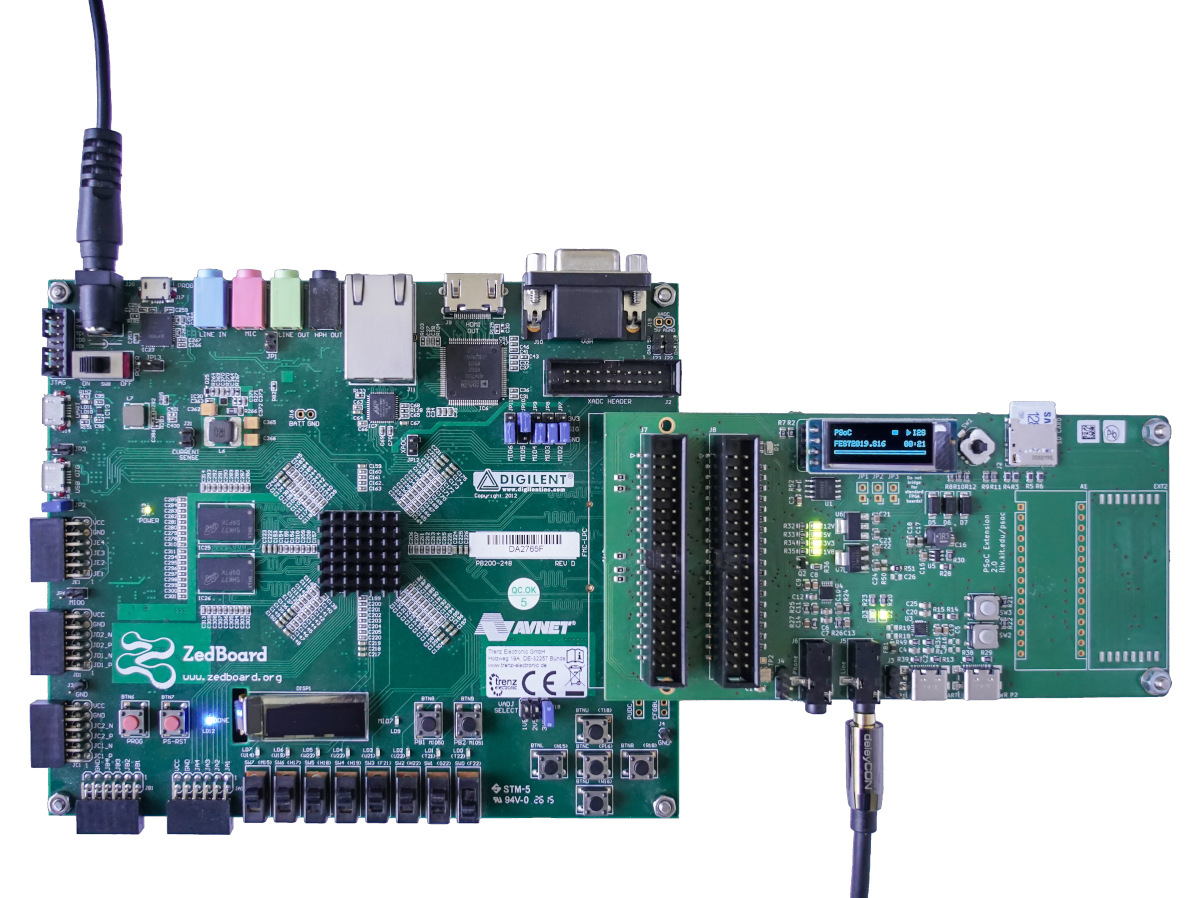

A simple open-source audio player firmware demonstrates the SoC’s capabilities. It reads audio files from a FAT-formatted SD card using FatFS and plays them via an external I2S DAC or the integrated Delta-Sigma Modulator. The application includes an I2C OLED display and joystick button for input, with debug output available over UART.

The Lab Course

The design presented so far is used as a base platform for the KIT System-on-Chip Lab. Students first implement RTL for simple peripherals and then extend the RISC-V SoC design to integrate their components. Furthermore, they learn to build custom Wishbone peripherals and access them using embedded C. The complete audio player is emulated on an FPGA platform in the lab and students can actually use the SoC and program it using custom code. Students also learn to simulate the design, synthesize it using OpenROAD for IHP SG13G2, and perform floorplanning, macro placement, and DRC checks.

The course also includes analog amplifier design and integration of analog cells into the digital design. After covering the basics, students spend half the semester developing and implementing their own ideas.

KCH Contribution

Teaching materials for the course are largely developed by ITIV staff. KCH contributed several technical key components to make get the course reference design ready for tapeout:

- Developed a peripheral to switch pin functions (primary/secondary and input/output)

- Implemented JTAG-SPI for programming external SPI flash via JTAG

- Ported the design to IHP OpenPDK SRAM (single port) and IO pads

- Performed floorplanning and macro placement

- Finalized the design for OpenROAD RTL2GDS

- Achieved DRC clean status and managed the tapeout via IHP’s September 2025 OpenMPW run

- Designed carrier PCBs

- Finalized the audio player firmware

- Open-sourced and documented all components

- Produced figures and promotional material

Further Information

Please refer to our GitHub repositories for more information:

- The SoC design: https://github.com/kit-kch/psoc-soc

- The Audio Player: https://github.com/kit-kch/psoc-sw-player

- Sign up for the PSoC course: https://itiv.kit.edu/psoc