V.Sh.Melikyan, V.M.Movsisyan, Sh.E.Bozoyan, S.H.Simonyan, R.R.Vardanyan, H.B.Maranjyan, V.V.Buniatyan, S.Kh.Khudaverdyan, S.G.Petrosyan, A.H.Babayan, A.G.Harutyunyan, M.G.Travajyan, V.S.Yeghiazaryan, H.A.Gomtsyan, M.A.Muradyan, G.E.Ayvazyan, V.A.Vardanyan, S.V.Melkonyan, A.K.Minasyan, A.K.Tumanyan, H.L.Stepanyan, H.G.Tananyan

# ANNUAL ARMENIAN MICROELECTRONICS OLYMPIAD TESTS AND PROBLEMS

# Welcome!

The problem book that you hold in your hands is the latest contribution of Armenia to the advancement of microelectronics. I am sure you will find it very modern, and useful. This is the book of tests and problems of the Annual Armenian Microelectronics Olympiad. At the same time, it will also be a very valuable resource for students, Masters and PhDs of microelectronics and similar engineering disciplines, providing them an opportunity to assess and improve their knowledge, as well as to develop solution skills of tests and problems.

The results of the First to the Fourth Olympiad witnessed that the book has served its purpose and has become "a table book" for participants.

As the third problem book of tests and problems focused on the development of Armenia's IT sector, it is a unique contribution in the key area of training highly qualified specialists. It will also contribute to the realization of the goals of the next Annual Armenian Microelectronics Olympiads, contributing to the ascension of Armenian microelectronics to a state-of-the-art and leading branch of industry.

It is my sincere hope this problem book will take its notable place in your professional library.

Richard Joldman With best wishes Rich Goldman, Vice president for Corporate Marketing of Synopsys Inc., CEO of Synopsys Armenia CJSC, President of Armenian Microelectronics Olympiad Organizing Committee, Honorable Doctor of SEUA

#### PREFACE

During the last three years the First (September 22-25, 2006), the Second (September 18-25, 2007), the Third (September 16-29, 2008) and the Fourth (September 15-30, 2009) Armenian Microelectronics Olympiads took place (http://www.microolymp.am). The goals of organizing the Armenian Microelectronics Olympiad were to: stimulate the further development of microelectronics in Armenia, discover young, talented resources (University students and specialists of microelectronics area companies up to 30 years), increase interest towards microelectronics among them, understand the level of knowledge in the field of microelectronics among young specialists to make necessary adjustments to educational programs in the future. Considering the successful experience of holding the Armenian Microelectronics Olympiads, it has become continuous, annual. It is not excluded that the Olympiad becomes international in the coming years. The success of the previous Olympiads was mainly conditioned by the finance assistance and huge organizational efforts of its main sponsor SYNOPSYS ARMENIA CJSC (CEO Rich Goldman, General Manager Hovik Musayelyan) and sponsors VIVACELL-MTS/K-Telekom CJSC (General Manager Ralph Yirikyan), USAID CAPS project (coordinator of IT cluster Armen Abrahamyan), Enterprise Incubator Foundation (director Bagrat Yengibanryan), ACBA bank (president Stepan Gishyan), Unicomp CJSC (director Armen Baldryan), Microsoft RA LTD (General Manager Grigor Barseghyan), Arminco CJSC (General Manager Andranik Aleksanyan), Virage Logic International Corporation (Executive Director Varuzhan Meserejyan), Union of Manufacturers & Businessmen of Armenia (UMBA) (Executive President Arsen Ghazaryan), Viasphere Technopark CJSC (General Manager Aram Vardanyan), Apaven Ltd (Director Gagik Makaryan), Union of Information Technology Enterprises (UITE) (Executive Director Karen Vardanyan), web-site developer "N-Sourcer" TM "Art Site" (Director Areg Harutyunyan), Yerkir Media TV Company (Director of media and political part Gegham Manukyan), ARKA Agency (Director Konstantin Petrosov), Mediastyle LTD (General Manager Vardan Asatryan), Ekonomika Magazine (Editor-in-Chief Lyusya Mehrabyan), "Delovoy Express" Weekly (Editor-in-Chief Eduard Naghdalyan), "168 Hours" Daily (Editor-in-Chief Satenik Seyranyan). In the sense of providing participants great assistance has been demonstrated by universities: SEUA (rector Vostanik Marukhyan, pro-rector Ruben Aghgashyan), YSU (rector Aram Simonyan, pro-rector Aleksandr Grigoryan), Russian-Armenian (Slavonic) State University (rector Armen Darbinyan, pro-rector Gagik Sargsyan), as well as Heads of Companies: SYNOPSYS ARMENIA CJSC (CEO Rich Goldman, General Manager Hovik Musayelyan), Instigate Inc. (Director Vahagn Sargsyan) as well as Gyumri Information Technologies Center (Executive Director Jason Kazarian). The first stage of the Olympiad was at the same time held in Gyumri for the first time. I express my deep gratitude to the mentioned people as well as the rest of the members of Organizing Committee of the Armenian Microelectronics Olympiads -Andranik Hovhannisyan (Deputy General Manager of SYNOPSYS ARMENIA CJSC), Vladimir Harutyunyan (Head of YSU microelectronics Chair), Harutyun Terzyan (SEUA Professor), Eduard Ghazaryan (Head of department of Russian-Armenian (Slavonic) State University), Andranik Aleksanyan (General Manager of Arminco CJSC), members of Program Committee Valeri Vardanyan (Scientific Worker of Virage Logic Corporation), David Parent (Associate Professor of San-Jose State University (USA, CA)), Slavik Melkonyan (YSU Professor), Artur Minasyan (Senior Engineer in SONICS ARMENIA HOLDINGS Armenian Design Center), as well as Gayane Markosyan who illustrated the event (SEUA Associate Professor, Senior Coordinator of SYNOPSYS ARMENIA CJSC Educational Department).

The Olympiads were held giving the participants a test with easy questions (the first stage) and problems requiring peculiar solutions (the second stage). Test questions and problems together with their solutions set in the from I-IV Armenian Annual Microelectronics Olympiads are included in the book. Test questions and problems are related to VLSI Design and EDA areas. They are classified according to the basic sections of the above mentioned areas.

- 1. Digital integrated circuits

- 2. Analog integrated circuits

- 3. RF integrated circuits

- 4. Semiconductor physics and electronic devices

- 5. Semiconductor technology

- 6. Numerical methods and optimization

- 7. Discrete mathematics and theory of combinations

- 8. Object-oriented programming

The problem book, first of all, is anticipated for the future participants of the Armenian Microelectronics Olympiad of the coming years. In my opinion, it will contribute to the increase of knowledge level of Olympiad participants. At the same time, it can also be useful for other students, Masters, PhDs and engineers of the above mentioned areas.

The problem book also contains to some extent similar test questions and problems as they have been included in different, equivalent variants during the Olympiads.

The problem book, in its future publications, will be filled with the test questions and problems of the coming Olympiads.

You can send your remarks at microelectronics\_olympiad@synopsys.com.

I express my deep gratitude to the below mentioned authors of the problem book most of whom are also members of Olympiad Program Committee.

- Vilyam Movsisyan Associate Professor of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA, PhD

- Shura Bozoyan Professor of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA, Sci.D.

- Sargis Simonyan Head of SEUA Dataware of Technical Systems Chair, Sci.D., Professor

- Ruben Vardanyan Head of SEUA Computer-Aided Design Chair, Sci.D., Professor

- Hrant Marandjyan Senior Engineer of Synopsys ARMENIA CJSC, Sci.D., Professor

- Vahe Buniatyan Head of SEUA Microelectronic and Biomedical Devices Chair, Sci.D., Professor

- Suren Khudaverdyan Head of SEUA Construction and Production of Radio Equipment Chair, Sci.D., Professor

- Stepan Petrosyan Deputy minister of diaspora of RA, Sci.D., Professor

- Armenak Babayan Associate Professor of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA, PhD

- Ashot Harutyunyan Associate Professor of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA, PhD

- Misak Travajyan Associate Professor of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA, PhD

- Hovhannes Gomtsyan Associate Professor of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA, PhD

- Movses Muradyan Senior lecturer of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA

- Vladimir Yeghiazaryan Dean of RAU Applied Mathematics and Informatics faculty, PhD, Associate Professor

- Gagik Ayvazyan Director of Semiconductor R & D Center of Viasphere Technopark CJSC, PhD

- Valery Vardanyan Scientific Worker of Virage Logic, PhD

- Slavik Melkonyan YSU Professor, Sci.D.

- Artur Minasyan Leading Engineer of Armenia Design Center of Sonics Armenia Holdings

- Anna Tumanyan Associate Professor of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA, PhD

- Harutyun Stepanyan Lecturer of Microelectronic Circuits and Systems Interdepartmental Chair of SEUA

Formatting of the problem book has been realized by:

- Eduard Babayan University Program Coordinator of SYNOPSYS ARMENIA CJSC

- Ruzanna Goroyan University Program Coordinator of SYNOPSYS ARMENIA CJSC

- Hayk Sargsyan (title page) Senior Engineer of SYNOPSYS ARMENIA CJSC

whom I also express my deep gratitude.

# Author and editor

President of Program Committee of Annual Armenian Microelectronics Olympiad, Director of SYNOPSYS ARMENIA CJSC Educational Department, Head of SEUA Microelectronic Circuits and Systems Interdepartmental Chair, Honorable Scientist of Armenia,

Sci.D., Professor Vazgen Shavarsh Melikyan

1. Mic bogund

# **TESTS AND PROBLEMS**

# **1. DIGITAL INTEGRATED CIRCUITS**

# a) Test questions

- **1a1.** There is tri-state buffer, in which internal delays can be ignored. Right after z state is set, the output voltage level will be:

- A. VDD/2, where VDD is supply voltage

- B. High or low, depending on the state before z state is set

- C. Indefinite

- D. High

- E. Low

- 1a2. In CMOS ICs, p MOS transistor is usually configured as:

- A. No potential is given to substrate

- B. Substrate is connected to source

- C. Substrate is connected to drain

- D. The highest potential is given to substrate

- E. The lowest potential is given to substrate

- **1a3.** There is JK flip-flop. Mark the prohibited input combination

- A. J=1, K=1

- B. J=1, K=0

- C. J=0, K=1

- D. J=0, K=0

- E. No prohibited combination

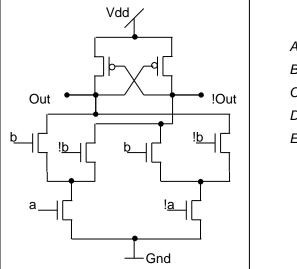

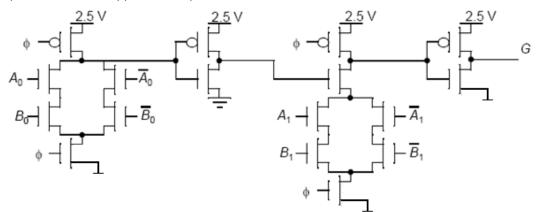

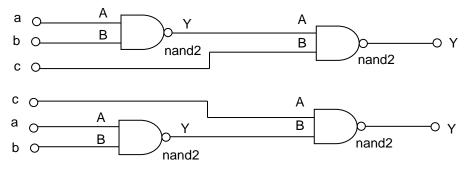

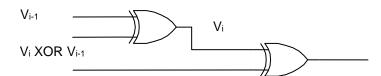

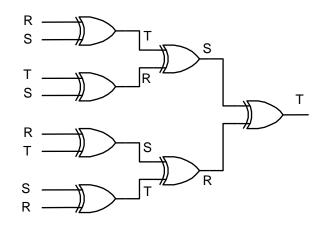

- 1a4. What logic function is implemented by the shown circuit?

A. AND B. XOR-XNOR C. AND-NAND D. OR-NOR E. MUX-MUXI

**1a5.** Which is the Canonical Disjunctive Normal Form (CDNF) of the function described by the following truth table?

|   | Output |   |   |

|---|--------|---|---|

| а | b      | С | у |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 0 |

| 0 | 1      | 0 | 1 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 0 |

| 1 | 0      | 1 | 0 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 1 |

*A. y*=!a&b&!c+!a&b&c+a&b&!c+a&b&c

B. y=!a&!b&!c+!a&!b&c+a&!b&!c+a&!b&c

C. y=(a+b+c)&(a+b+!c)&(!a+b+c)&(!a+b+!c)

D. y = (!a+!b+!c) & (!a+!b+c) & (a+!b+!c) & (a+!b+c)

*E*. y=(a+!b+c)&(a+!b+!c)&(!a+!b+c)&(!a+!b+!c)

- **1a6.** Threshold voltage of MOS transistor is called the voltage which is necessary to be applied between the gate and the source:

- A. For 1uA current flow through drain

- B. Of the transistor for current flow through drain which is 10 times more then leakage current of transistor

- C. Of the transistor for average concentration of charge carriers that maintain transistor's conductance be equal to average concentration of majority charge carriers in substrate in channel formation place

- D. Of the transistor for average concentration of charge carriers that maintain transistor's conductance be equal to average concentration of minority charge carriers in substrate in channel formation place

- E. Of the transistor for the transistor to be saturated

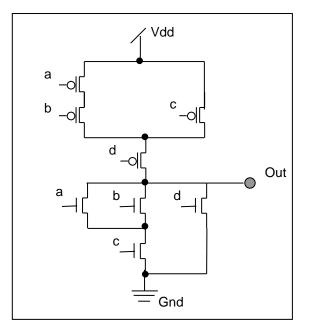

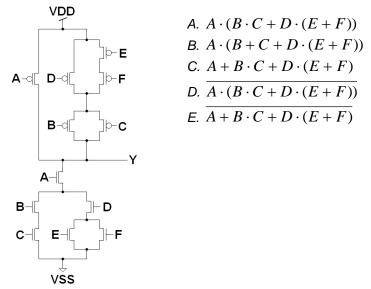

- 1a7. What formula describes the circuit?

- A. Out = !((!a+!b)&!c+!d)

- B. Out = !((a+b)&c+d)

- C. Out = !((a&b+c)&d)

- D. Out = ((!a+!b)&!c+!d)

- *E.* Out = !((!a&!b+!c)&!d)

- **1a8.** Which statement is correct?

- A. Charge-coupled devices' (CCD) work is based on processes occurring in bipolar transistors

- B. CCD's frequency internal limit is influenced by thermo generation of charge carriers

- C. CCD's frequency parameters do not depend on the degree of semiconductor's surface energetic levels

- D. CCD's frequency properties do not depend on the type of semiconductor

- E. CCDs are static devices

- **1a9.** Which of the shown answers more contributes to the successful solution of cells' placing problem?

- A. Maximum distance between high frequency circuits

- B. Maximum distance between low frequency circuits

- C. Maximum proximity of more related cells

- D. A. and C. together

- E. B. and C. together

- **1a10.** One of the rules of concurrent modeling is

- A.  $Lc(\gamma)$  list defined for an external output line composes the set of testable faults which can be found by the given input set (vector)

- B. Single stuck-at fault (SSF) model assume that there is only one fault in tested logic circuit

- C. Two types of stuck-at logic faults stuck-at-1 fault (SA1 or s@1) and stuck-at-0 fault (SA0 or s@0)

- D.  $Lc(\gamma)$  list defined for an external output line composes the set of testable faults which can be found by an output set (vector)

- E. None

- 1a11. In state-of-the-art integrated circuits the minimum width of interconnect's transmission lines is limited by

- A. Resolution of the lithography process

- B. Mutual agreement of customer and manufacturer

- C. The desire of designer

- D. Technological method to get thin layers

- E. The phenomena of electromigration

- The increase of the logic circuit organization's parallelism mostly leads to 1a12.

- A. The increase of performance

B. The increase of the number of primary outputs

C. The decrease of the number of logic cells

- D. A. and B. together

- E. B. and C. together

- 1a13. The  $f(x_1, x_2, x_3)$  function accepts 1 value on 0, 3, 5, 6 combinations. What class does the given function belong to?

- A. Constant 0

- B. Constant 1

- C. Linear and dual

- D. Dual

- E. Monotone

- **1a14.** Operation of Gunn diode is based on

- A. The effect of semiconductor inversion in strong electrical field

- B. The appearance of negative differential impedance in strong electrical field

- C. The tunnel effect in strong electric field

- D. The rectifying properties of p-n junction

- E. The contact effects between metal and semiconductor

- 1a15 Which of the shown answers more contributes to the increase of the fan-out?

- A. Increase of cells' input resistance

- B. Increase of cells' output resistance

- C. Decrease of cells' output resistance

- D. A. and B. together

- E. A. and C. together

- 1a16. Which of the following statements is wrong for synchronous FSM?

- A. Memory element competition, static and dynamic risks in combinational circuits are dangerous

- B. The abstract presentation of the automaton is used for building circuit

- C. Required synchronization of asynchronous input signals with clock signals

- D. All FFs trigger at the same clock signal

- E. The wrong answer is missing

- **1a17.** The common emitter configuration compared with common base configuration

- A. Increases frequency properties

- B. Increases the collector junction's resistance

- C. Increases collector junction's breakdown voltage

- D. Increases the current gain

- E. Decreases the thermal component of collector current

- 1a18. Which of following methods of interconnect designing more contributes to speed increase? A. Increase of interconnect layers

- B. Decrease of total length of interconnects

- C. Decrease of length of signal processing critical path

- D. B. and C. together

- E. A. and C. together

- 1a19. Among the following principles, which is wrong for concurrent simulation?

- Α. Classification of vectors according to quality, move low quality vectors in the beginning of simulation, elimination of detected faults - it increases simulation speed, reduces simulation time

- B. Any subset of faults is simulated, extrapolation of fault coverage is executed according to obtained results

- C. IC simulation, estimation of vectors' quality 01 or 10 toggle node number, toggle coverage

- D. For the given vector there is strict correlation between detectable fault number and 01, 10 toggle number

- E. None

- **1a20.** There is an inverter which has a passive capacitive load. If supply voltage increases,

- A. Rise will increase, Fall will decrease

- B. Fall will increase, Rise will decrease

- C. Output transition time will decrease

- D. Output transition time will increase, as during switching the load must be charged by larger □ U voltage

- *E.* Output transition time will remain the same, as U will increase, but charging current will also increase

- **1a21.** The transfer characteristic of MOS transistor is *the dependence of:*

- A. Drain voltage on gate-source voltage

- B. Drain voltage on drain-source voltage

- C. Drain current on drain-source voltage

- D. Drain current on gate-source voltage

- E. Gate current on gate-source voltage

- **1a22.** Latch up phenomena is proper to

- A. ECL circuits

- B. Only CMOS circuits

- C. N-MOS and CMOS circuits

- D. P-MOS and CMOS circuits

- E. All bipolar circuits

- **1a23.** Which one is prohibited input combination for RS latch?

- A . R=0, S=1

- B. R=1, S=0

- C. R=0, S=0

- D. R=1, S=1

- E. There is no prohibited combination

- **1a24.** Define in which state will Johnson's 6 bit counter go, after the 10<sup>th</sup> pulse is applied. Initial state is 000111.

- A. 011110,

- B. 001011,

- C. 101010,

- D. 011010,

- E. The correct answer is missing

- 1a25. How many pins does the bipolar transistor have?

- A. 1- emitter,

- B. 2- emitter and base,

- C. 2- base and collector,

- D. 2- emitter and collector;

- E. 3- emitter, base and collector,

- **1a26.** What semiconductor material is mostly used in integrated circuits?

- A. Ge

- B. Si

- C. GaAs

- D. Fe

- E. Zn

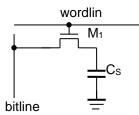

- 1a27. From the following statements which is wrong for DRAM?

- A. Usually one MOS transistor is used to keep 1 bit in memory

- B. FF is as a memory cell

- C. Address inputs are multiplexed

- D. DRAMs are considered energy dependent

- E. The wrong answer is missing

- **1a28.** In logic design level the following is designed:

- A. Stand alone device which is divided up to such multibit blocks as registers, counters, etc

- B. Stand alone logic gate or FF, which consists of electronic components transistors, diodes, etc

- C. Stand alone semiconductor component, e.g. transistor

- D. Digital device the components of which are separate logic gates and FFs

- E. General system which consists of RAM memory device, datapath devices, etc

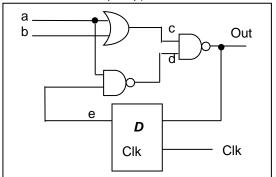

- **1a29.** Identify the synchronous model of the following circuit. (TP- delays, TF-transition time, "p"-previous state of flip-flop).

- A. c=a & b, d=!(a | e), Out=!(c & d), e=posedge(Clk ? Out: 'p'), TP=0.1n, B. c=a | b

- d=!(a | e), Out=!(c & d), e=posedge(Clk) ? Out: 'p'

- C. c=a & b, b=!(a | e), Out=!(c & d), e=!(posedge(Clk)? Out: 'p'), TF=0.1n

- D. c=a & b, TP=0.1n, d=!(a | e), TP=0.1n, Out=!(c & d), TP=0.1n, e=posedge(Clk) ? Out: 'p', TP=0.1n, E. c=a & b, TP=0.1n, d a l a TP=0.1n,

- d=a | e, TP=0.1n, Out=c & d, TP=0.1n, e=!(posedge(Clk)? Out: 'p'), TP=0.1n,

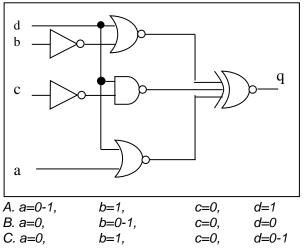

- 1a30. In case of which switching the occurrence of dynamic fail risk is possible in the following circuit?

| D. a=1,   | b=0, | c=1, | d=0-1 |

|-----------|------|------|-------|

| E. a=0-1, | b=0, | c=1, | d=0   |

- **1a31.** In component level of the design the following is being designed:

- A. A separate semiconductor device, e.g. transistor

- B. A separate device, which is being disassembled until diverse components, such as registers, calculators, etc

- C. A separate logic gate or FF which consists of electronic components transistors, diodes, etc

- D. A general system which consists of operative memory device, numerical device, etc

- E. A digital device which consists of separate logic gates and FFs

- 1a32. In order to prevent latch-up in CMOS circuits it is necessary

- A. To increase the parasitic capacitances between the buses of output buffer's parasitic bipolar transistors

- B. To increase the gain of parasitic bipolar transistors

- C. Put the drains of n and p transistors as close as possible

- D. Put n+ guard ring around n+ source/drain

- E. Put p+ guard ring around n+ source/drain and put n+ guard ring around p+ source/drain

- 1a33. In digital circuits p-MOS transistor's

- A. Delays do not depend on the supply voltage

- B. Threshold voltage is proportional to the delay of transistor

- C. Delays do not depend on temperature

- D. The highest potential is usually applied to substrate

- E. Dynamic power dissipation depends only on transistor resistance

- **1a34.** For the following circuit mention the input which will have the maximum input-to-output delay.

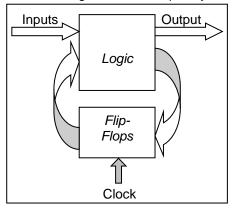

**1a35.** In the following digital system, where setup time of FF is T<sub>SU</sub>, delay T<sub>CLKQ</sub>, and delay of logic part T<sub>LOGIC</sub>, the highest clock frequency will be

A.  $f=1 / T_{LOGIC}$ B.  $f=1 / (T_{LOGIC}+T_{SU})$ C.  $f=1 / (T_{LOGIC}+T_{CLKQ}+T_{SU})$ D.  $f=T_{LOGIC}+T_{CLKQ}+T_{SU}$ E.  $f=1 / (T_{LOGIC}+2^{*}T_{CLKQ}+T_{SU})$

- **1a36.** Which is the sum of the following two signed hexadecimal numbers if the addition is performed by saturation adder: 81H + FEH?

- A. 7FH

- B. FFH

- C. 00H

- D. 80H

- E. 77H

- **1a37.** Which of the following is the binary representation of 3.25 decimal number in 4bit, 4bit fixed point format?

- A. 01110101

- B. 10001010

- C. 00110100

- D. 00111010

- E. 01111001

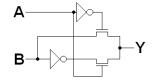

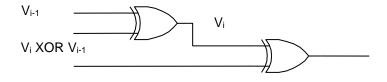

- 1a38. XOR logic circuit is shown in the figure. Which is the disadvantage of the circuit?

- A. Input capacitances are large

- B. Delays are large

- C. Output 1 level is degradated

- D. Output 0 level is degradated

- E. Power consumption is large

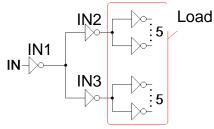

- **1a39.** Buffer circuit composed by I1, I2, I3 identical inverters is shown in the figure. The I2 and I3 are loaded by 5 similar inverters. What expression is the average delay of the buffer defined by?

- A.  $(R_p + R_n) \cdot (2 \cdot C_{out} + 7 \cdot C_{in})$

- $B. \quad (R_p + R_n) \cdot (5 \cdot C_{out} + 7 \cdot C_{in})$

- C.  $(R_p + R_n) \cdot (C_{out} + 7 \cdot C_{in})$

- $D. \quad 2 \cdot (R_p + R_n) \cdot (2 \cdot C_{out} + 7 \cdot C_{in})$

- $E. \quad (R_p + R_n) \cdot (2 \cdot C_{out} + 5 \cdot C_{in})$

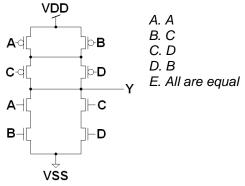

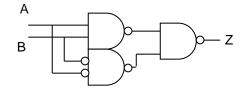

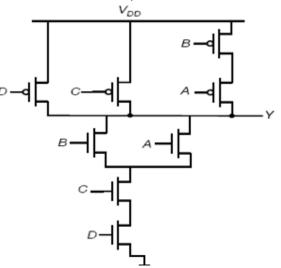

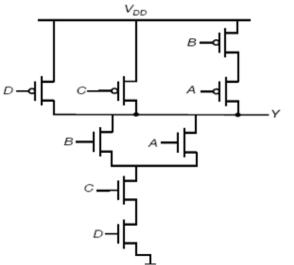

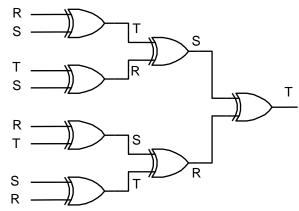

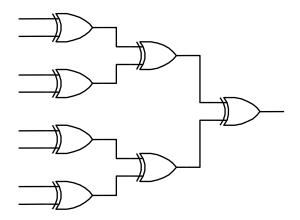

1a40. What logic function is realized in the shown circuit?

1a41. What formula does the given circuit describe?

- A. Z=A&B+(!A&!B)

- $B. \quad Z=(!A\&B)+(!B\&A)$

- D. Z=A&(!B) E. Z=A+!B

- 1a42. Saturation condition of NMOS transistor has the following view:

- $\begin{array}{l} \text{A. } V_{DS} \leq V_{GS} V_{THN} \\ \text{B. } V_{DS} \geq V_{GS} V_{SB} \\ \text{C. } V_{GS} \geq V_{DS} V_{THN} \\ \text{D. } V_{DS} \geq V_{GS} V_{THN} \\ \text{E. } V_{DS} \geq V_{GS} + V_{THN} \end{array}$

- 1a43. Conjunctive Normal Form (CNF) of the function in the following truth table has the following view:

| а | b | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

- A. (!a+!b+!c)& (!a+b+c)& (!a+b+c)& (!a+!b+c)

- B. (a+!b+!c)& (!a+b+c)& (!a+b+c)& (!a+!b+!c)

- C. (!a+!b+c)& (!a+!b+c)& (!a+b+c)& (!a+!b+c)

- D. (a+b+c)& (!a+b+c)& (!a+b+!c)& (!a+!b+c)

- E. !a&!b&!c+ !a&b&!c+ a&!b&!c+ a&b&c

- **1a44.** In what state will the below shown automaton go after applying four pulses if the initial state is Q1Q2=1x?

- A. 01

- B. 10

- C. 00 D. 11

- E. x1

- **1a45** In digital circuits, for an n-MOS transistor *A. The lowest potential is usually given to substrate*

- B. Delays do not depend on the supply voltage

- C. Threshold voltage is proportional to the delay of transistor

- D. Delays do not depend on temperature

- E. Dynamic power dissipation depends only on transistor resistance

- **1a46.** Which is the sum of the following two signed hexadecimal numbers if the addition is performed by saturation adder: 12H + 70H?

- A. 7FH

- B. FFH

- C. 00H

- D. 80H

- E. 82H

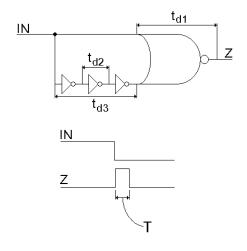

- **1a47.** T duration of the short pulse, obtained on the output of the given circuit, is mainly defined by?

A. td1 B. td3 C. td2 D. td1 + td2 E. td1 + td3 delays.

**1a48.** If A and B are interpreted as two-bit binary words, A = {A1, A0} and B = {B1, B0} then what interpretation can be applied to output G?

- A. Scalar product: G=(A0&B0)+(A1&B1)

- B. Modulo-2 sum:  $G=(A0 \oplus B0) \oplus (A1 \oplus B1)$

- C. Equality: G = (A = B)

- D. Non-equality G=(A != B)

- E. Logic sum G=A0+B0+A1+B1

- **1a49.** Considering that NOR2 cell's inputs are independent and equally distributed, which is the probability of output switching?

- A. 0.25 B. 0.375 C. 0.5 D. 0.75

- E. 0.875

- **1a50.** Assuming  $k_n=2k_p$ , in what case will the resistances from the output of NOR2 cell to VDD and VSS be equal?

- A.  $W_p = W_n$

- B.  $W_p = 2W_n$

- C.  $W_p = 4W_n$

- D.  $W_{p}=6W_{n}$

- E.  $W_p = 8W_n$

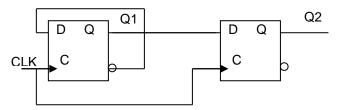

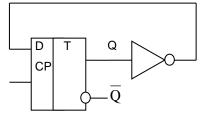

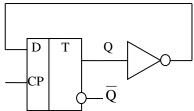

- 1a51. The figure shows the circuit of frequency divider.

What expression gives the minimum period of clock pulses?

- A.  $T_{min}=t_{su}+t_{c2q}+t_{pinv}$

- B.  $T_{min} = t_{c2q} + t_{pinv}$

- C.  $T_{min} = t_{su} + t_{hd} + t_{c2q} + t_{pinv}$

- D.  $T_{min} = t_{hd} + t_{c2q} + t_{pinv}$

- E.  $T_{min} = t_{su} + t_{hd} + t_{pinv}$

- **1a52.** How many digits does the thermometer code have which is obtained after modifying 4-bit binary code?

- A. 16

- B. 4

- C. 15

- D. 8

- E. 32

- 1a53. For the same size inverter what version has minimum leakage current?

- A. PMOS low-vt, NMOS high-vt

- B. PMOS standard-vt, NMOS high-vt

- C. PMOS high-vt, NMOS standard-vt

- D. PMOS high-vt, NMOS low-vt

- E. PMOS low-vt, NMOS standard-vt

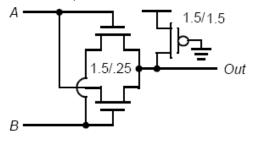

- 1a54. What logic function does the circuit implement?

- A.OUT=A+B B.OUT=A&B C.OUT=!A+!B D.OUT=!A&!B E.OUT=A⊕!B

- **1a55**. Which is the basic consequence of MOS transistor's degradation due to warm carriers? *A. The increase of threshold voltage*

- *B.* The decrease of threshold voltage

- C. The increase of channel resistance

- D. The decrease of channel resistance

- E. The decrease of drain-package disruption voltage

- **1a56**. Assuming k<sub>n</sub>=rk<sub>p</sub>, in what case will the resistances from the output of 3NAND cell to VDD and VSS be equal?

- A.  $W_p/W_n = r$

- B.  $W_{p}/W_{n}=r/9$

- $C W_{p}/W_{n}=r/6$

- D.  $W_{p}/W_{n}=r/3$

- E.  $W_p/W_n=2r/3$

#### 1a57. Which one of the given expressions is wrong?

- *A*. *A*⊕!*B* = !*A*⊕*B*

- B.  $1 \oplus ! B \oplus A = B \oplus A$

- *C. A⊕B* =! *A⊕*!*B*

- D.  $A \oplus !B = !A \oplus !B$

- *E.* !*A*⊕*B* = !(*A*⊕*B*)

- **1a58**. What is the minimum number of transistors in a pass gate implemented 1:4 multiplexer, assuming that normal and complemented select variables are available:

- A. 16

- B. 12

- C. 8

- D. 6

- E. 4

- 1a59. What function does the circuit implement?

- A. OUT=A+B

- B. OUT=A&B

- C. OUT=!A+!B

- D. OUT=!A&!B

- E. OUT=A⊕!B

- **1a60**. C capacitance is connected to the end of interconnect line with L length, line parameters are c [F/m], r [Ohm/m]. By what formula is the signal delay time in the line given?

- A. 0.7rc B. 0.7Lr(C+c) C. 0.7Lr(C+Lc/2) D. 0.7Lr(C+Lc)

- E. 0.7Lr(C/2+Lc/2)

- 1a61. By increasing the metal line length of interconnect in IC, the delay increases *A. Linearly B. By square law C. By 3/2 law*

- D. By 2/3 law

- E. By cubic law

- **1a62.** In what case is the short connection current missing in CMOS inverter? A.  $V_{tp}=V_{tn}$

- B.  $V_{tp}+V_{tn}=0$ C.  $V_{tp}+V_{tn} < VDD$ D.  $|V_{tp}|+V_{tn} < VDD$ E.  $|V_{tp}|+V_{tn} < VDD/2$

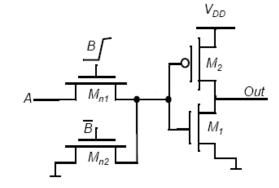

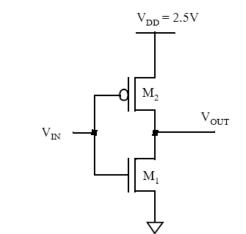

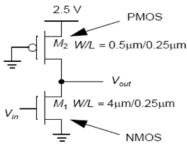

- **1a63**. Which answer is true, if  $V_{IN}=V_{DD}$ ?

A.M1-saturated, M2-linear B. M1-linear, M2-linear C.M1- linear, M2- saturated D. M1-saturated, M2-saturated E. None

- 1a64. In what case is short connection current missing in CMOS inverter?

- A.  $V_{tp}=V_{tn}$

- B.  $V_{tp}+V_{tn}=0$

- C.  $V_{tp}+V_{tn} < VDD$

- $D. |V_{tp}|+V_{tn} < VDD$

- E.  $|V_{tp}|+V_{tn} < VDD/2$

- 1a65. What equation describes JK flip-flop junctions?

- A. Q = Q J + Q K

- $B. \ Q+=!Q\&J+Q\&K$

- C. Q +=!Q&J + Q&!K

- D. Q = Q | J + ! Q | K

- E. Q+=Q&J + !Q&!K

- **1a66.** At passing from one technology to the other, transistors are scaled by S <1 coefficient due to which the gate capacitance of a transistor with minimal sizes, depending on S:

- A. Increases linearly

- B. Decreases linearly

- C. Increases by square law

- D. Decreases by square law

- E. Does not change

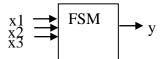

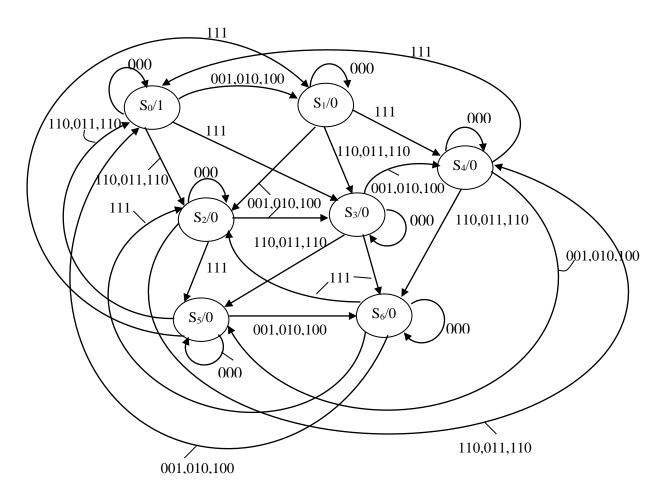

- **1a67**. Given a circuit of synchronous FSM, detector of an input sequence. Perform FSM analysis.

Determine which input sequence the given FSM detects. The end of the previous word may be a beginning of the next one.

- A. 0110

- B. 1001

- C. 0100

- D. 1101

- E. The correct answer is missing

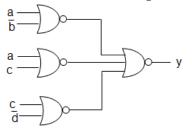

- 1a68. Given a circuit in NOR basis. What function does the given circuit implement?

- A.  $\overline{a} \cdot b + \overline{a} \cdot \overline{c} + \overline{c} \cdot d$

- B.  $a \cdot c + \overline{b} \cdot c + a \cdot \overline{d}$

- C.  $b \cdot c \cdot \overline{d} + \overline{a} \cdot b + c \cdot d$

- D.  $\overline{a} \cdot b \cdot \overline{d} + a \cdot \overline{b} + c \cdot d$

- E. The correct answer is missing

- **1a69**. What is the difference of electrical "short" or "long" interconnects at most characterized by?

- A. Interconnect width

- B. Signal power

- C. Signal edge increase

- D. Current power

- E. A. and B. together

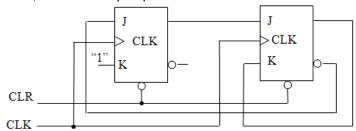

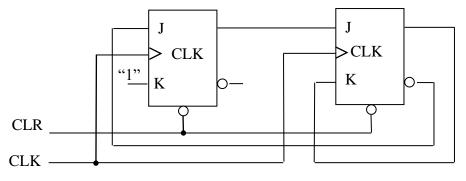

- 1a70. Analyze FSM circuit, built on JK-flip-flops.

Which of the listed functions realizes the given circuit?

- A. It is a modulo-4 binary up counter

- B. It is a modulo-3 binary up counter

- C. It is a modulo-4 binary down counter

- D. It is a modulo-3 binary down counter

- E. The correct answer is missing

- **1a71.** In case of the shown element base, what is the order of power reduction of the circuit? a) bipolar; b) CMOS; c) N-MOS

- A. a-c-b

- В. b-с-а

- С. а-b-с

- D. b-a-c

- Е. с-b-а

- **1a72.** Required to construct 64:1 multiplexer using 8:1 multiplexer. How many 8:1 multiplexers are needed?

- A. 8 MUX 8:1

- B. 9 MUX 8:1

- C. 10 MUX 4:1

- D. 11 MUX 8:1

- E. The correct answer is missing

- **1a73.** Which of the below listed criteria of organizing interconnects, more contributes to the increase of performance?

- A. Increase of the number of interconnects layers

- B. Similarity of interconnects length

- C. Increase of the number of vias

- D. Reduction of critical path of signal processing

- E. A. and B. together

- 1a74. The logic of which circuit presented by VHDL code is senseless or wrong?

- A. process (clock) begin  $Y \leq A$  and B; end process; B. process (A) begin  $A \le A + 1;$ end process; C. process (A) begin  $Y \le A + 1;$ end process; D. process (A, B) begin  $Y \leq A$  and B; end process; E. process (reset\_n, clock) begin  $i\bar{f}$  (reset\_n = '0') then Y <= 0;elsif (clock'EVENT and clock = '1') then  $Y \leq A$  and B; end if; end process;

- 1a75. Given F(x1,x2,x3) = x1⊕ x2⊕ x2⋅x3 function. Which of the given expressions corresponds to the given function?

- A.  $F = x1 \cdot \overline{x^2} + x1 \cdot x^3 + \overline{x^1} \cdot x^2 \cdot \overline{x^3}$ B.  $F = x1 \cdot x^2 + \overline{x^1} \cdot x^3 + \overline{x^1} \cdot x^2 \cdot \overline{x^3}$ C.  $F = \overline{x^1} \cdot \overline{x^2} + x1 \cdot x^2 + x^2 \cdot \overline{x^3}$ D.  $F = x1 \cdot \overline{x^2} + x^2 \cdot x^3 + x1 \cdot \overline{x^3} \cdot x^2$ E.  $F = x1 \cdot \overline{x^2} + x1 \cdot x^2 + x^2 \cdot \overline{x^3}$

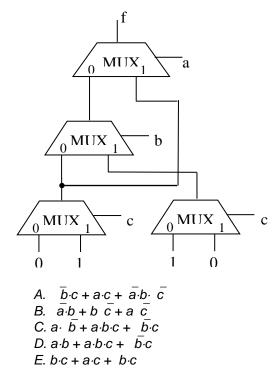

1a76. Which of the functions below is realized in the given circuit on multiplexer?

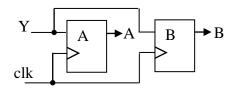

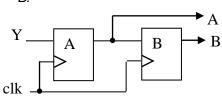

1a77. Analyze the FSM, designed on JK flip-flop.

What does the given FSM represent? A. 2-bit shift register B. polynomial counter C. subtractive bitwise counter modulo 4 D. additive bitwise counter modulo 3

*E. subtractive bitwise counter modulo* 3

1a78. Which circuit does the use of the following assignment correspond to?

E. None of the circuits corresponds to the assignment.

1a79. In case of what transition of input signal, the circuit output does not switch, and X node switches?

A. AB=00->01 B. AB=00->11 C. AB=01->10 D. AB=11->00 E. AB=10->00

- **1a80.** For what purpose is created Low-Doped-Drain (LDD) region? A. to increase threshold voltage B.to increase saturation voltage C. to increase gate-source break-down voltage D. to reduce gate capacitance

- E. to increase gate's oxide break-down voltage

- **1a81.** The first stage of the 12-input 2-stage decoder is implemented by 3AND cells, and the second one by 4AND cells. How many 3AND cells are there in the first stage?

- A. 16

- B. 24

- C. 32

- D. 8

- E. 64

- **1a82.** Considering that memory array has equal number of 1-bit cells in lines and columns, define how many word lines does 10 address bit memory has if the word length is 4 bits.

- A. 32

- B. 64

- C. 128 D. 1024

- E. 256

- 1a83. What logic function does the circuit implement?

- B. g<sub>1</sub>=AB+C, g<sub>2</sub>=(AB+C)(E+D) C. g<sub>1</sub>=AB+C, g<sub>2</sub>=(AB+C)ED D. g<sub>1</sub>=AB⊕C, g<sub>2</sub>=(AB⊕C)ED

- *E.*  $g_1 = AB + C$ ,  $g_2 = (AB + C)$  (*E* $\oplus$ *D*)

# b) Problems

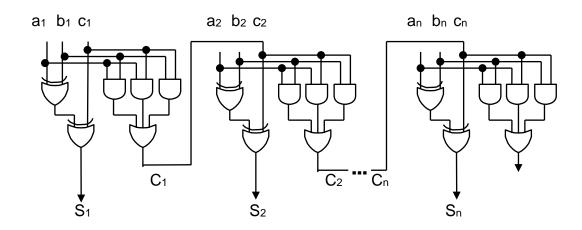

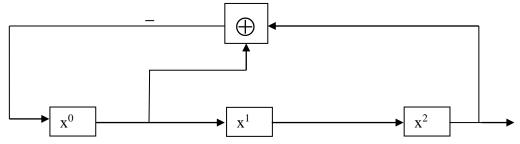

# 1b1.

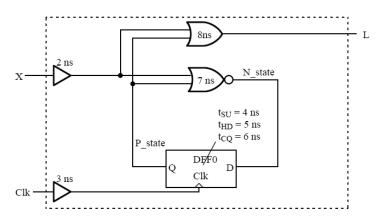

For the shown circuit:

- a. What are the external setup and hold times for input X?

- **b.** What is the delay from the clock to output L?

- c. What is the clock cycle time based on register-to-register delays? (flip flop is drawn "backwards").

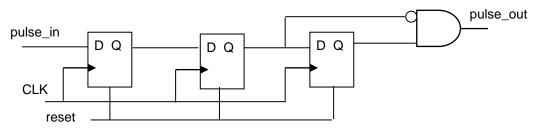

# 1b2.

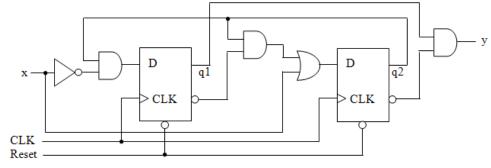

Consider the following VHDL code. library ieee: use ieee.std\_logic\_1164.all; entity pulsedet is port( signal clk,reset,pulse\_in: in std\_logic; signal pulse\_out: out std\_logic ); end pulsedet; architecture behavior of pulsedet is signal dffout : std\_logic\_vector(2 downto 0); begin dffs: process(clk,reset) begin if (reset = '1') then dffout <= "000"; elsif (clk'event and clk='1') then  $dffout(2) \le dffout(1);$  $dffout(1) \le dffout(0);$ dffout(0) <= pulse\_in; end if: end process; pulse out  $\leq$  dffout(2) and not dffout(1); end behavior:

Draw a diagram of logic that implements the VHDL code. (Show logic gates and D flip-flops.)

#### 1b3.

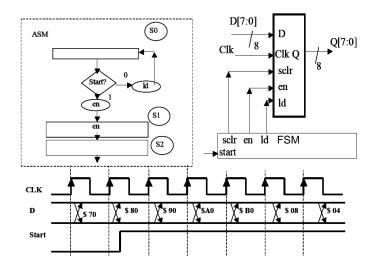

On the waveforms below, complete the waveforms for State, Id, en, and Q. The FSM is controlling the UP counter. Assume the initial state is S0.

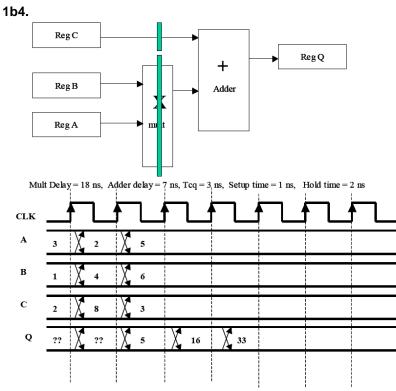

# 1b4.

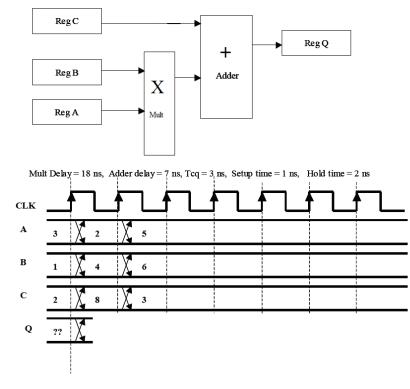

For the figure below:

a. Give the maximum register-to-register delay.

b. Modify the diagram to add one level of pipelining but still maintain the same functionality. Add the pipeline stage in the place that will improve the register-to-register delay the most. Compute the new maximum register-to-register. Assume that adding a pipeline registers to any functional unit (adder or multiplier) breaks the combinational delay path in the unit exactly in half.

c. With the pipeline stage added, complete the 'Q' waveform shown below. Input registers change values as shown; assume Reg Q is loaded every clock cycle. All waveforms represent register outputs.

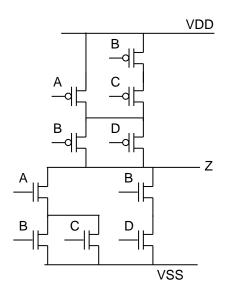

# 1b5.

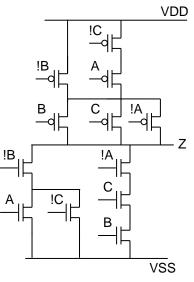

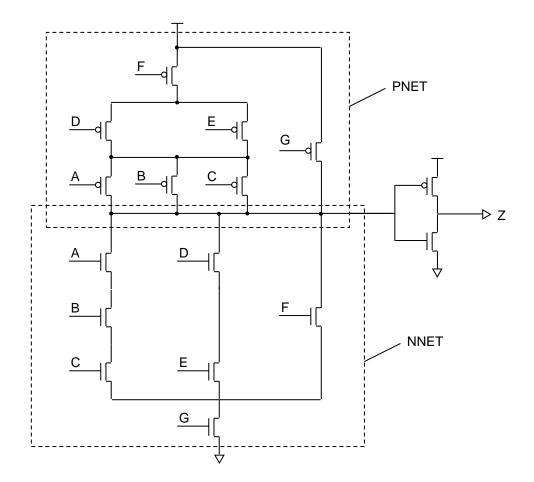

Build the circuit for CMOS cell which is realized by

Z=!(A(B+C)+BD)

logic function.

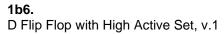

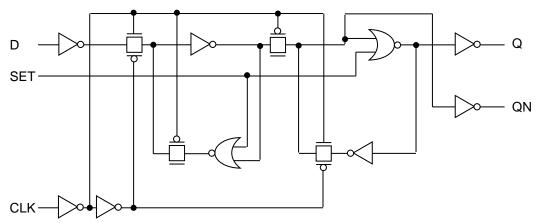

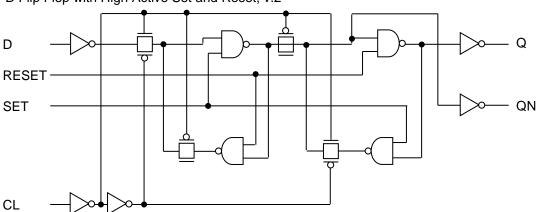

**1b6.** Build MS D-FF based on transmission gates (TG) with SET input.

# 1b7.

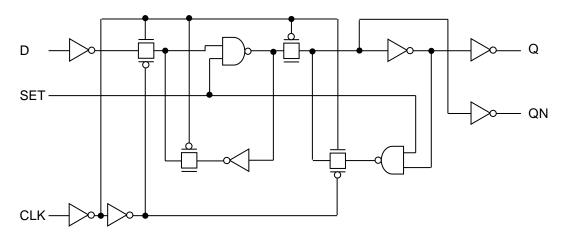

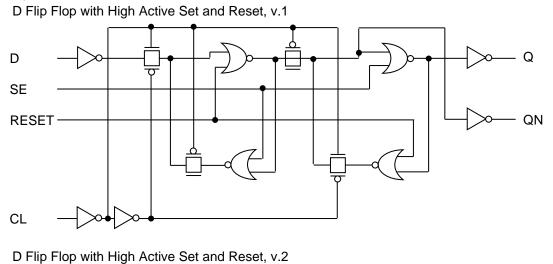

Build MS D-FF based on switching keys with SET and RESET inputs.

# 1b8.

Build CMOS cell circuit which is described by  $Y=\sum(1,2,6,7)$  function.

#### 1b9.

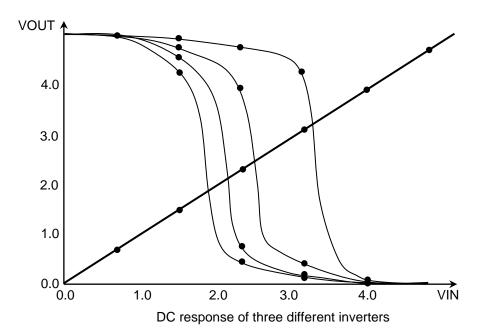

Four inverters (VDD=5V) have WN, changing from 3um to 12um while WP is the same for each inverter (10 um).

Identify which WP/WN ratio produces the most left curve in Figure 1.

In this process VDD is 5V. Which inverter has the most even noise margins ( $V_{THN}$ =0.6 V,  $V_{THP}$ =-0.8 V, LN=LP)?

#### 1b10.

Both circuits below have the same function. Which one has the smallest, best case delay? Explain the answer for full credit.

#### 1b11.

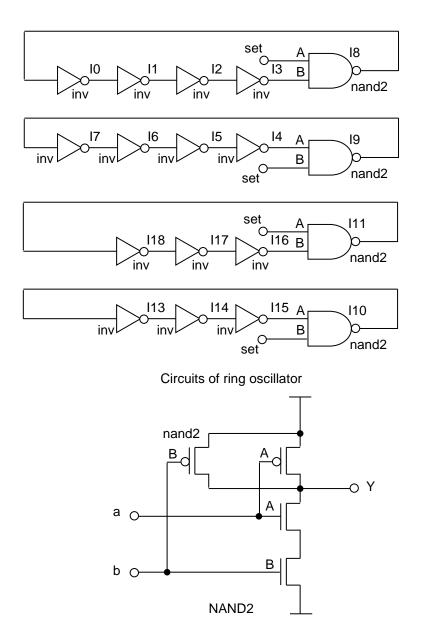

It is necessary to design a ring oscillator that is to oscillate as fast as possible. Usually a set pin is needed to start the ring oscillator properly. Which circuit would be used for the fastest ring oscillator? Explain why for full credit.

# 1b12.

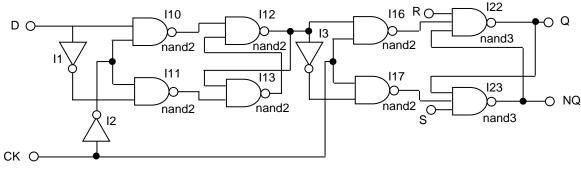

Figure shows a DFF. Using the timing data presented in the table, calculate how long CK has to remain high for Q and NQ to get the value from the output of I12 (nand2).

Figure shows a DFF. Using the timing data presented in the table, calculate how long D has to remain stable before the rising clock edge so that the outputs of I12 and I13 properly get the value of D (or not(D)).

DFF

Table: Various times for various gates.

|            | INV | NAND2 | NAND3 |

|------------|-----|-------|-------|

| TFALL (ps) | 200 | 500   | 600   |

| TRISE (ps) | 300 | 500   | 650   |

| τphl (ps)  | 100 | 250   | 300   |

| τplh (ps)  | 150 | 250   | 325   |

# 1b13.

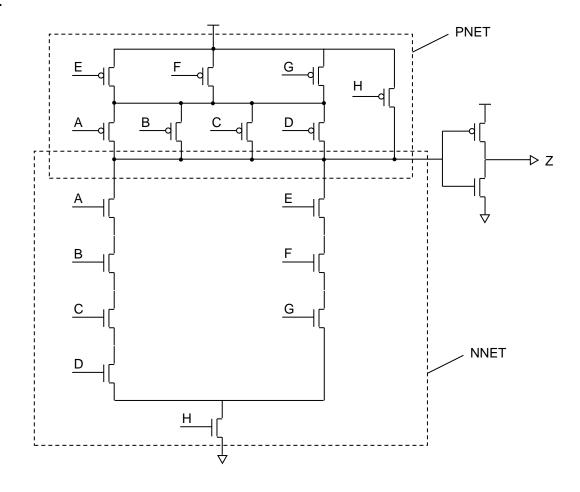

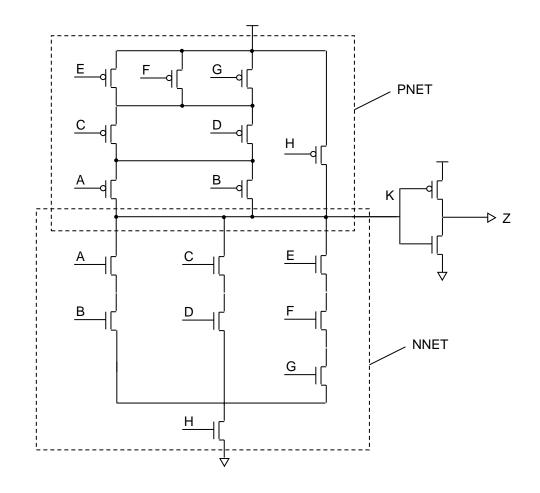

Using the AOI technique design a CMOS circuit to implement the following logic function: Z=(ABCD+EFG)HShow the PNET and the NNET connected into a circuit.

# 1b14.

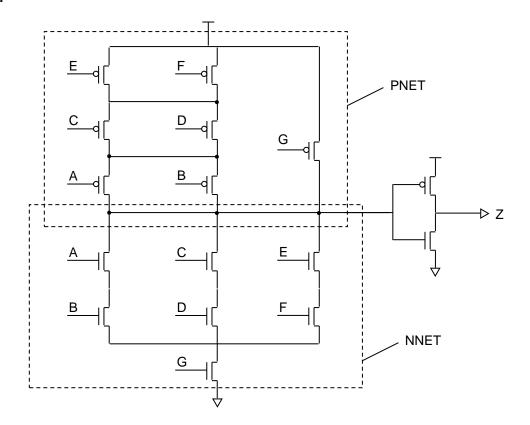

Using the AOI technique, design a CMOS circuit to implement the following logic function: Z=(AB+CD+EF)GShow the PNET and the NNET connected into a circuit.

# 1b15.

Using the AOI technique, design a CMOS circuit to implement the following logic function: Z=(AB+CD+EF)GShow the PNET and the NNET connected into a circuit.

# 1b16.

Using the AOI technique, design a CMOS circuit to implement the following logic function: Minimize area and delay. (Show Euler path, but do not draw it).

Z=(AB+CD+EFG)H

Show the PNET and the NNET connected into a circuit.

For reading the bitline is precharged to VDD/2. Determine the settled voltage on the bitline when reading logic 1 and logic 0, if Vtn=0.3V, VDD=1.2V,  $C_{BL}$ =10C<sub>s.</sub> The voltage swing of the wordline control is from 0 to VDD. Ignore leakages and body bias effect.

#### 1b18.

Compute the following for the pseudo-NMOS inverter shown below:

$k_n = 115 uA/V^2$ ,  $k_p = 30 uA/V^2$ ,  $V_{tN} = 0.5 V$ ,  $V_{tP} = -0.4 V$

- a) Vol and Voh

- b) The static power dissipation: (1) for V<sub>in</sub> low, and (2) for V<sub>in</sub> high

- c) For an output load of 1 pF, calculate t<sub>pLH</sub>, t<sub>pHL</sub> (ignore the intrinsic capacitances of transistors)

#### 1b19.

Consider the circuit below.

- a) What is the logic function implemented by the CMOS transistor network? Size the NMOS and PMOS devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 4 and PMOS W/L = 8.

- b) What are the input patterns that give the worst case *tpHL* and *tpLH*. State clearly what are the initial input patterns and which input(s) has to make a transition in order to achieve this maximum propagation delay. Consider the effect of the capacitances at the internal nodes.

1b20.

If P(A=1)=0.5, P(B=1)=0.2, P(C=1)=0.3 and P(D=1)=0.8, determine the switching power dissipation in the logic gate. Assume *VDD*=2.5V, *Cout*=30fF and *fclk*=250MHz.

#### 1b21.

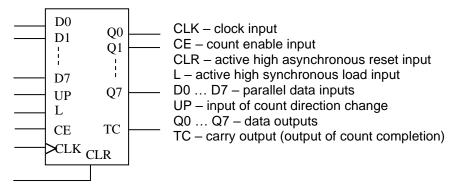

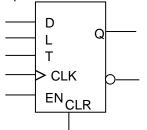

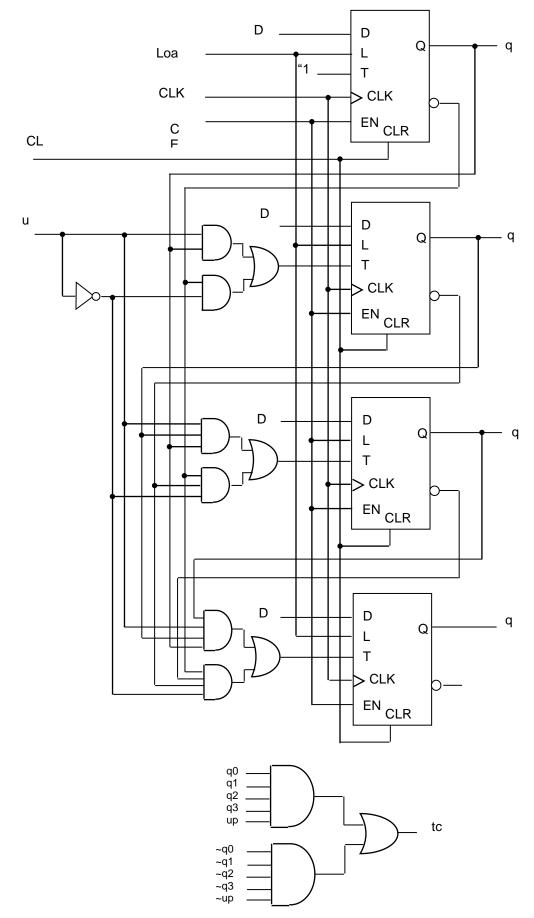

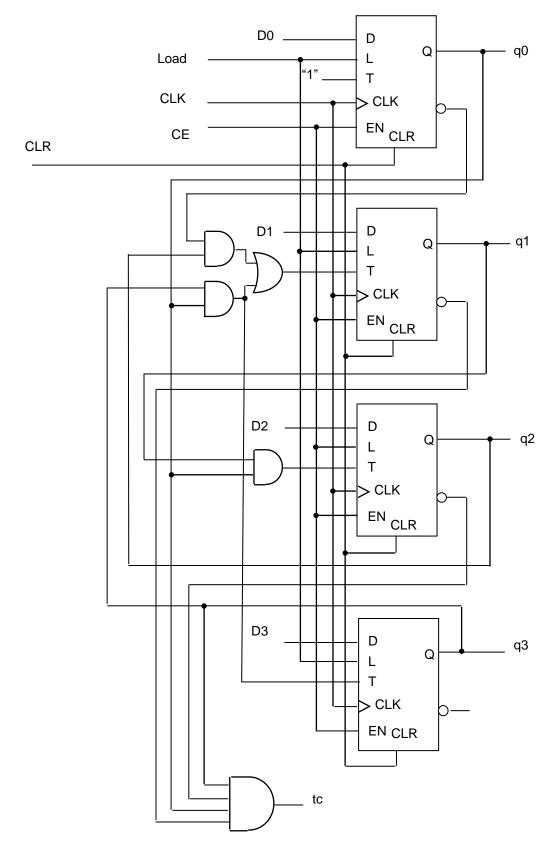

Design 8-bit binary up/down counter with parallel synchronous loading, asynchronous reset and an input to enable counting.

Logic symbol for the given counter:

TC is set as soon as code FF<sub>16</sub> or 00<sub>16</sub> appears on counter outputs.

| CLR | L | CE | UP | CLK | Q7 Q0                           | TC  | Mode                           |

|-----|---|----|----|-----|---------------------------------|-----|--------------------------------|

| 1   | Х | Х  | Х  | Х   | 0 0                             | 0   | Asynchronous reset             |

| 0   | 1 | Х  | Х  |     | D7 D0                           | 0   | Parallel loading (D[7:0]≠FF)   |

| 0   | 1 | Х  | Х  |     | D7 D0                           | 1   | Parallel loading (D[7:0] =FF)  |

| 0   | 1 | Х  | Х  |     | D7 D0                           | 1   | Parallel loading (D[7:0] ≠00)) |

| 0   | 1 | Х  | Х  |     | D7 D0                           | 1   | Parallel loading (D[7:0] =00)  |

| 0   | 0 | 1  | 1  |     | +1                              | 0   | Increment (Q[7:0] ≠FF)         |

| 0   | 0 | 1  | 1  |     | +1                              | 1   | Increment (Q[7:0] =FF)         |

| 0   | 0 | 1  | 0  |     | -1                              | 0   | Decrement (Q[7:0]) ≠ 00)       |

| 0   | 0 | 1  | 0  |     | -1                              | 1   | Decrement $(Q[7:0]) = 00)$     |

| 0   | 0 | 1  | 0  | Х   | Q7 <sub>n</sub> Q0 <sub>n</sub> | TCn | Hold                           |

#### Truth table of the counter

$Q7_n \dots Q0_n$  – previous states of the counter.

a) Describe counter in Verilog and Simulate using logic analysis tool VCS.

- b) Synthesize using Design Compiler tool. Obtain Verilog-out (Gate Level Netlist). Again simulate and compare the results.

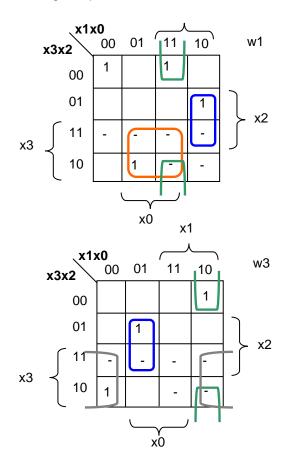

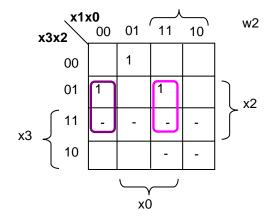

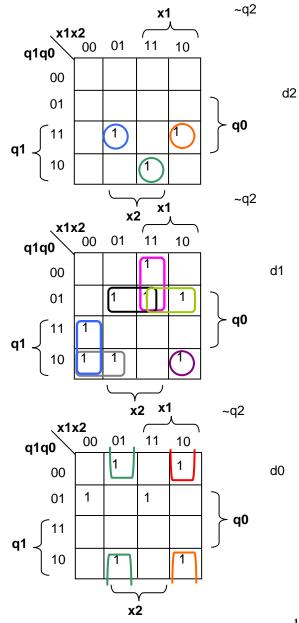

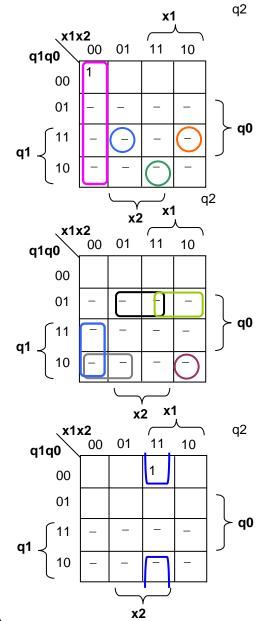

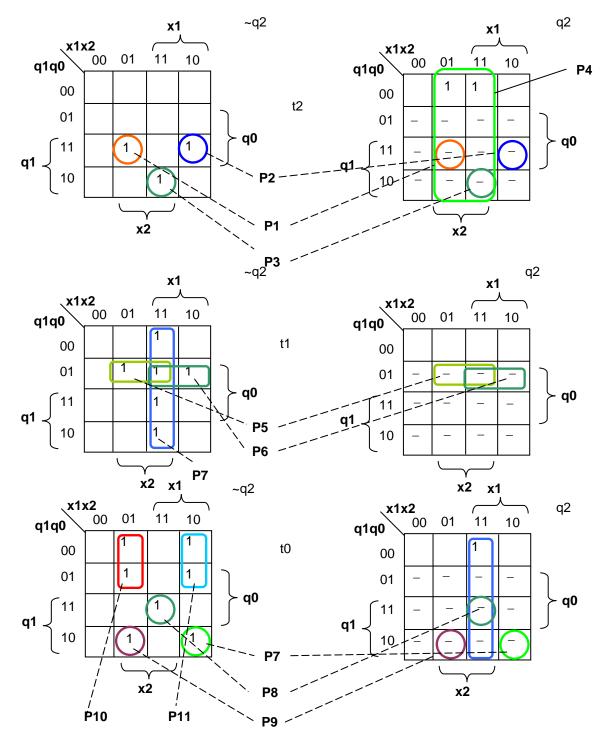

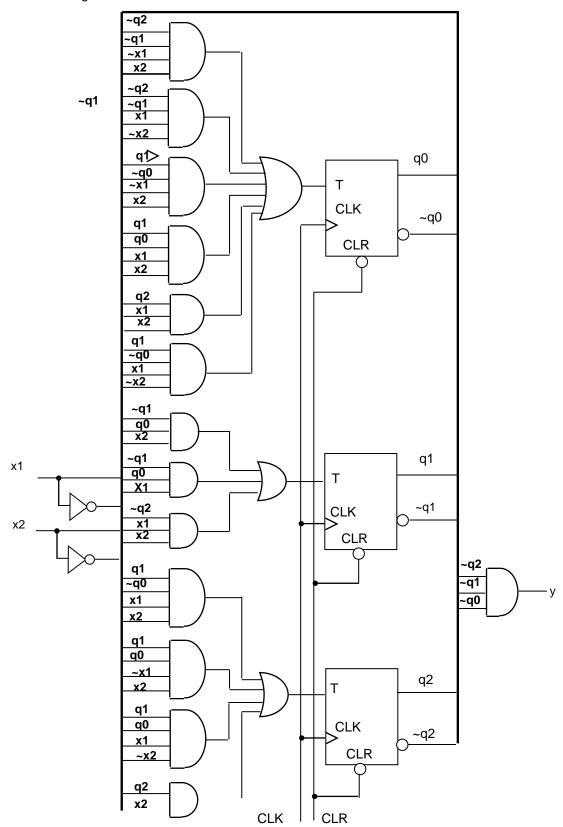

- c) Synthesize the circuit of the given counter manually, using T flip-flops. For simplification take the number of bits equal to 4.

# 1b22.

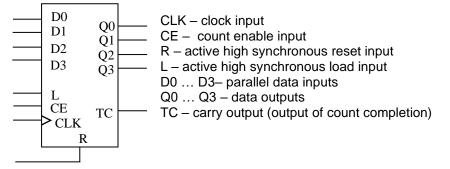

Design 4-bit binary-coded decimal counter with parallel synchronous loading, synchronous reset and count enable inputs.

Logic symbol for the given counter:

TC is set as soon as code 1001<sub>2</sub> appears on counter outputs.

Truth table of the counter

| R | L | CE | CLK        | Q3 Q0                           | TC  | Mode                            |

|---|---|----|------------|---------------------------------|-----|---------------------------------|

| 1 | Х | Х  | $\uparrow$ | 0 0                             | 0   | Synchronous reset               |

| 0 | 1 | Х  | $\uparrow$ | D3 D0                           | 0   | Parallel loading (D[3:0]≠1001)  |

| 0 | 1 | Х  | $\uparrow$ | D3 D0                           | 1   | Parallel loading (D[3:0] =1001) |

| 0 | 0 | 1  | $\uparrow$ | +1                              | 0   | Increment (Q[3:0]#FF)           |

| 0 | 0 | 1  | $\uparrow$ | +1                              | 1   | Increment (Q[3:0]=FF)           |

| 0 | 0 | 0  | Х          | Q3 <sub>n</sub> Q0 <sub>n</sub> | TCn | Hold                            |

$Q3_n...Q0_n$  – previous states of the counter.

- a) Describe counter in Verilog and Simulate using logic analysis tool VCS.

- b) Synthesize using Design Compiler tool. Obtain Verilog-out (Gate Level Netlist). Again simulate and compare the results.

- c) Synthesize the circuit of the given counter manually, using T flip-flops.

#### 1b23.

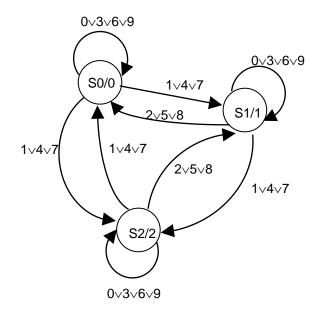

Design a clocked synchronous Moore FSM producing a remainder of division of a decimal number by 3 on its outputs. FSM receives the digits of a decimal number sequentially on its inputs.

- a) Describe counter in Verilog and Simulate using logic analysis tool VCS.

- b) Synthesize using Design Compiler tool. Obtain Verilog-out (Gate Level Netlist). Again simulate and compare the results.

- c) Synthesize the circuit of the given counter manually.

#### 1b24.

Design a clocked synchronous FSM with two inputs, X and Y, and one output, Z. The output should be 1 if the number of 1 inputs is the multiple of 5 on X and Y since reset, and 0 otherwise.

- a) Describe counter in Verilog and Simulate using logic analysis tool VCS.

- b) Synthesize using Design Compiler tool. Obtain Verilog-out (Gate Level Netlist). Again simulate and compare the results.

- c) Synthesize the circuit of the given counter manually.

#### 1b25.

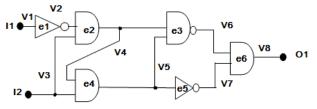

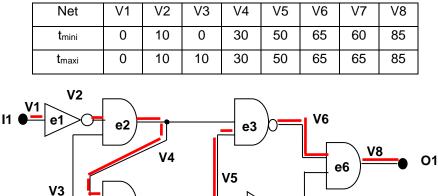

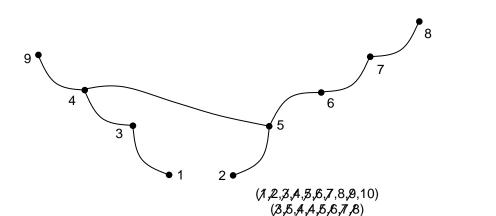

Calculate the minimum and maximum signal formation time of the shown circuit in  $V_1 - V_8$  nets by conventional units, if the cell delays are given by conventional units  $\tau_{e1}=\tau_{e5}=10$ ,  $\tau_{e3}=15$ ,  $\tau_{e2}=\tau_{e4}=\tau_{e6}=20$ : On the circuit mark I/O critical path and calculate the total delay of that path by conventional units.

# 1b26.

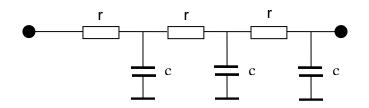

An interconnect of 300 um length and 0,2 um width is given, the sheet resistance and capacitance of which correspondingly equal:

$R_{\Box}$  =0,2 Ohm/ $_{\Box}$

C =0,1 fF/um.

Construct the equivalent circuit of interconnect's 3-segment, R,C distributed parameters and calculate the delay in it.

# 1b27.

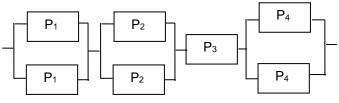

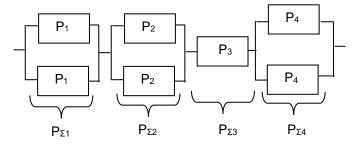

Calculate faultness probability of IC consisting of 7 blocks if their connection, according to reliability, has the following view.

Given P1=0.5; P2=0.6; P3=0.8; P4=0.4.

# 1b28.

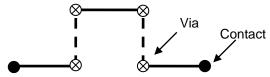

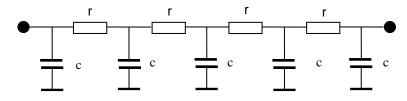

Two contacts are connected by an interconnect containing 4 vias, as illustrated in the figure.

Construct interconnect's R, C equivalent circuit and calculate the delay in the transmission line connecting two contacts, if given:

- Each transmission line's capacitance of interconnect equals 100 fF

– Each programmable contact resistance equals 1 Ohm.

Ignore ohmic resistances of transmission lines and contacts as well as the capacitances of vias.

# 1b29.

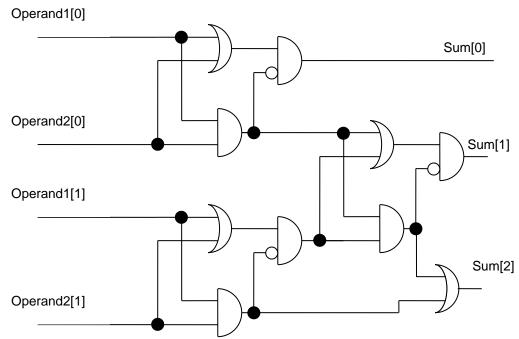

Based on the logic of provided VHDL code, develop digital circuit consisting of logic gates. library ieee;

```

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder2 is port(

signal

operand1,

operand2: in std_logic_vector(1 downto 0);

signal

sum: out std_logic_vector(2 downto 0);

);

end adder2;

architecture behavior of adder2 is

begin

sum <= operand1 + operand2;

end behavior;

```

Determine whether the provided logic is a combinational logic or not. Please argue the answer.

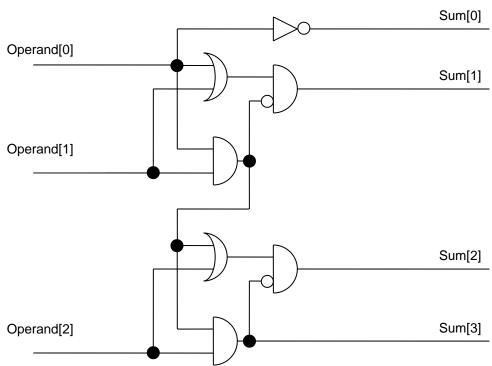

# 1b30.

Based on the logic of provided VHDL code, develop digital circuit consisting of logic gates. library ieee; use ieee.std\_logic\_1164.all; use ieee.std\_logic\_unsigned.all;

```

entity incr1 is port(

signal

operand: in std_logic_vector(2 downto 0);

signal

incr_result: out std_logic_vector(3 downto 0);

);

end incr1;

architecture behavior of incr1 is

begin

incr_result <= operand + 1;

end behavior;

Determine whether the provided logic is a combinational logic or not. Please argue the answer.</pre>

```

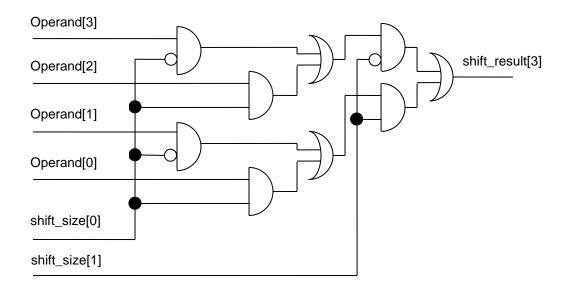

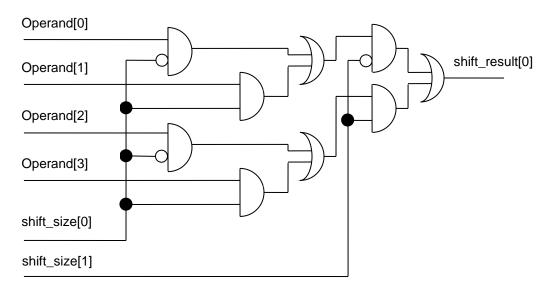

1b31.

Based on the logic of provided VHDL code, develop digital circuit consisting of logic gates. library ieee; use ieee.std\_logic\_1164.all; library types; use types.conversions.all; entity shift\_ll is port( signal operand: in std\_logic\_vector(3 downto 0); shift\_size: in std\_logic\_vector(1 downto 0); signal shift\_result: out std\_logic\_vector(3 downto 0); ); end shift II; architecture behavior of shift\_ll is begin process (operand, shift\_size) begin --left logical shift by shift\_size shift\_result <= operand sll to\_uint(shift\_size);</pre> end process; end behavior;

Determine whether the provided logic is a combinational logic or not. Please argue the answer.

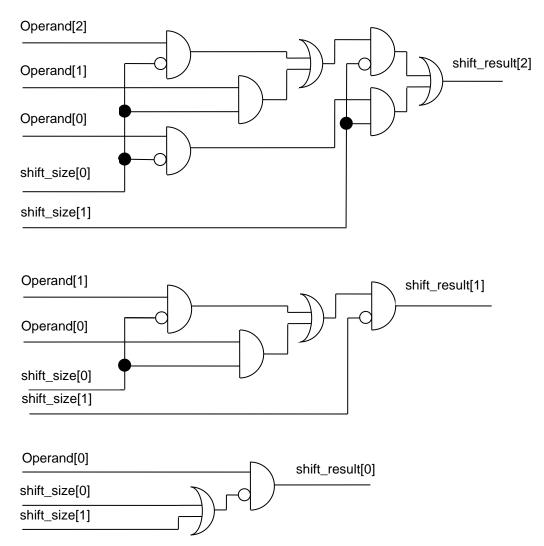

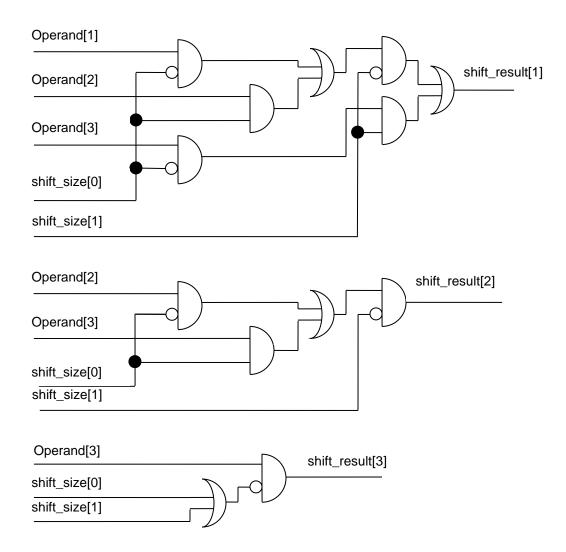

1b32.

```

Based on the logic of provided VHDL code, develop digital circuit consisting of logic gates.

library ieee;

use ieee.std_logic_1164.all;

library types;

use types.conversions.all;

entity shift_rl is port(

signal

operand: in std logic vector(3 downto 0);

shift_size: in std_logic_vector(1 downto 0);

signal

shift_result: out std_logic_vector(3 downto 0);

);

end shift_rl;

architecture behavior of shift_rl is

begin

process (operand, shift_size)

begin

--right logical shift by shift_size

shift_result <= operand srl to_uint(shift_size);</pre>

end process;

end behavior;

Determine whether the provided logic is a combinational logic or not. Please argue the answer.

```

1b33.

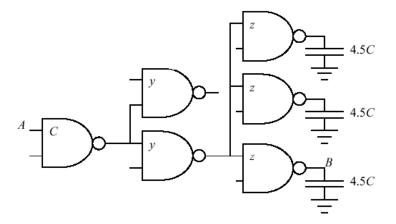

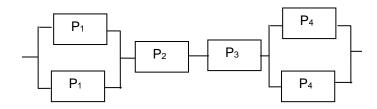

The sizes of the first cell in the shown logic circuit are selected in a way that it has a driving strength of a minimal size inverter having input capacitance C, i.e. NMOS transistor sizes have been increased to compensate the consequence of serial connection.

Define the second and third stages' scaling ratios y and z, from the condition to get minimum delay in the A-to-B path. Ignore intrinsic output and interconnects capacitances of cells.

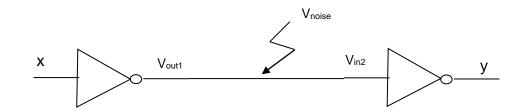

#### 1b34.

For the following circuit define the maximum allowable noise magnitude V<sub>noise</sub>, if the inverter's VTC parameters are V<sub>OHnom</sub>=1V, V<sub>OHmin</sub>=0.9V, V<sub>OLnom</sub>=0V, V<sub>OLmax</sub>=0.15V, V<sub>SP</sub>=048V, V<sub>IHmin</sub>=0.58V, V<sub>ILmax</sub>=0.44V.

#### 1b35.

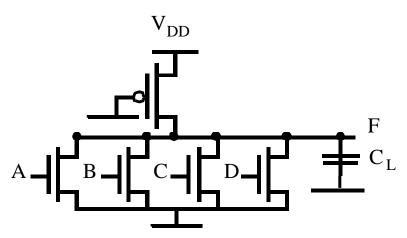

Define four input NOR cell's output low and high levels (see the figure) (a) when only one input switches, (b) when all the inputs switch simultaneously if  $C_L=0.05 \text{ pF}$ . Use the following technological parameters VDD=1.8 V,  $T_{ox}=10^{-8} \text{ m}$ ,  $\mu_n=270 \text{ cm}^2/\text{Vv}$ ,  $V_{tn}=0.5\text{V}$ ,  $\mu_p=70 \text{ cm}^2/\text{Vv}$ ,  $V_{tp}=-0.5\text{V}$ ,  $L_n=0.18 \text{ um}$ ,  $W_n=20 \text{ um}$ ,  $W_p=5 \text{ um}$ .

# **1b36.** Here a circuit of frequency divider is presented.

Define the minimum period of clock pulses, if t<sub>su</sub>=20ps, t<sub>hd</sub>=-15ps, t<sub>c2q</sub>=100ps, t<sub>pinv</sub>=30ps.

# 1b37.

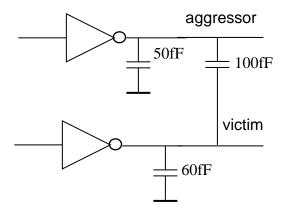

For the given circuit define:

a) maximum value of the noise in the victim line, which occurs when the signal in the aggressor line switching from 1.0 V to 0V.

b) effective capacitance of victim line for delay calculation if the signals in aggressor and victim lines are switching in opposite directions.

# 1b38.

Design Moore FSM which has 3 inputs x1, x2, x3 and 1 output. The output of FSM equals 1 when total number of ones, which are given to FSM inputs, is divided by 7.

Describe on Verilog. Create a testbench and simulate using VCS.

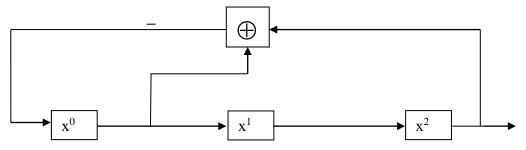

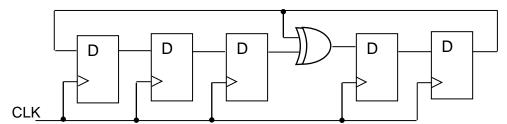

#### 1b39.

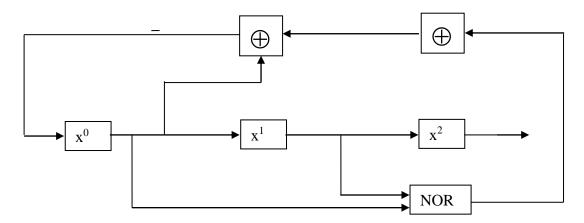

Describe on Verilog 5-bitpolynomial. In feedback circuit  $d(x) = 1 + x^3 + x^5$  is polynomial. The counter has 10000 initial state asynchronous preset input. The shift of information is realized by positive edge of clock signal.

Describe on Verilog. Create a testbench and simulate using VCS.

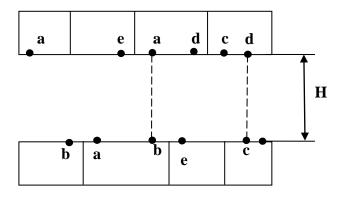

#### 1b40.

Define the minimum H distance between two rows of cells which is necessary for routing of two-layer coperpendicular routing of a, b, c, d, e nets if the minimum permissible size between interconnects width and space is 0,1 um, and the minimum distance between interconnects and 0,2 um.

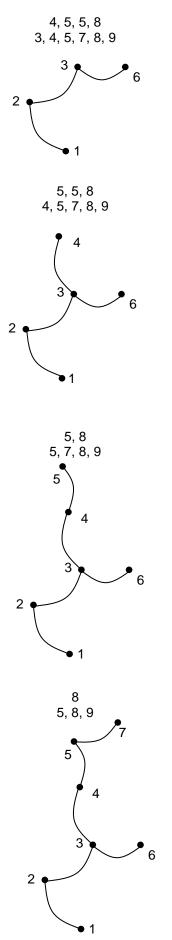

#### 1b41.

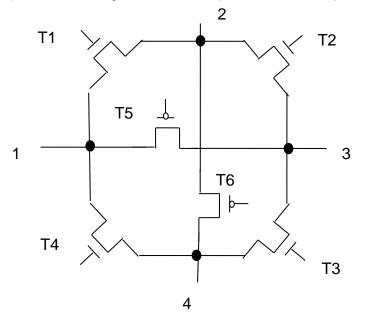

Switching block with 4 pins (1, 2, 3, 4) is shown in the figure. It consists of 4 N-MOS and 2 P-MOS transistors. What kind of logic level signals (0 or 1)should be given to each gate of T1-T6 transistors in order to provide:

a) simultaneous signal transfer from pin 1 to 3 and from pin 2 to 4;

b) simultaneous signal transfer from pin 1 to 4 and from pin 2 to 3;

# 1b42.

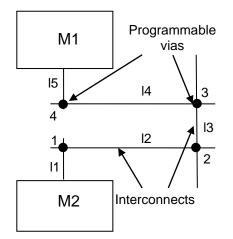

Two modules (M1 and M2) are connected with 5 interconnects (I1-I5) and 4 programmable vias (1-4). Construct interconnect's R, C equivalent circuit and calculate the delay in the transmission line connecting two modules, if given:

Each transmission line's capacitance of interconnect equals 100 fF

Each programmable contact resistance equals 1 Ohm.

Ignore ohmic resistances of interconnects and contacts as well as the capacitances of programmable vias.

# 1b43.

Calculate faultness probability of IC consisting of 7 blocks if their connection, according to reliability, has the following view.

Given P<sub>1</sub>=0,5; P<sub>2</sub>=0,6; P<sub>3</sub>=0,8; P<sub>4</sub>=0,4.

# 2. ANALOG INTEGRATED CIRCUITS

a) Test questions

- 2a1. How is the balancing of the differential amplifier executed?

- A. By applying additional biasing to one of inputs

- B. Through external potentiometer connected between load resistors of two branches

- C. By the change of supply voltage value

- D. A. and B. answers are correct

- E. All the answers are wrong

# 2a2. What differences are between inverting and non-inverting adders based on operational amplifier?

- A. Output signal's phase

- B. There is interaction of signal sources in inverting adder

- C. In inverting adder inputs are limited

- D. Interaction of signal sources is absent in inverting adder

- E. B. and C. answers are correct

- **2a3.** Input resistance for differential signal of differential amplifier can be increased by:

- A. The increase of resistors in emitter circuits

- B. The increase of transistors' $\beta$ s

- C. The application of Darlington's transistors

- D. The application of field transistors

- E. All the answers are correct

- **2a4.** What is the advantage of "R 2R" matrix towards "R 2R 4R 8R © © © © © " matrix in digitalanalog converters?

- A. More precise

- B. Can be multibit

- C. The current of reference voltage is constant

- D. Is being heated in a more uniform way

- E. All the answers are correct

- 2a5. Which analog-digital converter (ADC) is the fastest?

- A. Sequential ADC

- B. Parallel ADC

- C. Double integration ADC

- D. The speed depends on the applied cells

- E. The most high-speed is not mentioned among the answers

- **2a6.** Why does the increase of collector resistor value lead to transistor's saturation mode in a common emitter circuit?

- A. Because it leads to collector voltage increase

- B. Because it leads to base current increase

- C. Because it leads to collector current increase and contributes to transistor opening

- D. All the answers are correct

- E. All the answers are wrong.

- **2a7.** What is the differential amplifier's application limited by?

- A. Large input resistance

- B. Large output resistance

- C. The difference of input resistances for common mode and differential signals

- D. Large amplifier coefficient

- E. All the answers are correct

- 2a8. What is the reason of occurrence of disbalance of differential amplifier?

- A. Transistors of two branches are not similar

- B. Difference of resistance values between two branches

- C. The summary difference between both transistors and resistors of two branches

- D. Non ideal nature of the power source

- E. All the answers are correct

- **2a9.** What properties are being demonstrated by active integrator considered from the frequency point of view?

- A. High pass filter

- B. Low pass filter

- C. Band-pass filter

- D. Rejecter filter

- E. Has no filtering properties

- **2a10.** The random variable signal conversion accuracy of ADC depends on:

- A. Comparator accuracy

- B. Resistors accuracy in R-2R matrix of internal DAC

- C. Bit count of ADC

- D. Performance of ADC elements

- E. All the answers are correct

- 2a11. The quality of current source in differential amplifier depends on

- A. High internal resistance

- B. Thermostability

- C. Current value

- D. A, B, C answers are correct

- E. A, B answers are correct

- **2a12.** Analog IC production group method is based on the following factors:

- A. Parameter similarity of elements produced during the same technological process

- B. Elements on crystal, which are placed close to each other, heat evenly

- C. Elements thermal coefficient similarity

- D. A, B, C answers are correct

- E. Technological restrictions on element implementation

- 2a13. What is the minimum value of the resistance of OpAmp negative feedback limited by?

- A. Ku=1 request

- B. Thermal instability of input currentC. Permissible minimum value of resistance of OpAmp output load

- D. No limitation

- E. All the answers are wrong

- In voltage stabilizer by OpAmp application why is the feedback given to the inverse input not from 2a14. OpAmp output, but from the output of output emitter repeater

- A. To fade the loading of OpmAmp

- B. To fade stabilitron current given to the direct input

- C. To compensate thermal instability of the output emitter repeater

- D. To increase amplifier's coefficient of OpAmp

- E. All the answers are correct

- 2a15. What factors is the redundancy principle of analog microcircuitry based on?

- A. Technological restrictions of element preparation

- B. On those elements of the circuit which are not possible to carry out in crystal or occupy too much area, are substituted by multielement node which implements the same function.

- C. A.and B. answers are correct

- D. On placing redundant elements on crystal area

- E. Minimization of the number of circuit elements

- **2a16.** Why does not the emitter oscillate the voltage?

- A. Because the output voltage must always be smaller than the one of the input for open state of the transistor

- B. Because it is not possible to increase large nominal resistance in emitter circuit

- C. Because the output signal is taken from transistor's emitter

- D. Because the emitter repeater cannot provide large output resistance

- E. All the answers are correct

- 2a17. What is the role of additional emitter repeater in current mirror?

- A. Has no influence

- B. Increases the output current of current mirror

- C. Balances current mirror

- D. Increases the output resistance of current mirror

- E. All the answers are wrong

- 2a18. What is the comparator's sensibility, built on OpAmp, conditioned by?

- A. Input resistances of OpAmp

- B. Value of supply voltage

- C. Own amplifier's coefficient of OpAmp

- D. Debalance of OpAmp

- E. All the answers are wrong

- What is the advantage of double integration of ADC? 2a19.

- A. Increases the conversion accuracy

- B. Thermal stability

- C. Compensates the thermal instability of integrator's capacitor

- D. A., B. answers are correct

- E. A., B., C.answers are correct

- 2a20. Between what points is the input resistance for differential signal of differential amplifier distributed?

- A. Between inputs of differential amplifier

- B. Between inputs of differential amplifier and ground

- C. Between one input of differential amplifier and ground

- D. Between one input of differential amplifier and negative power source

- E. All the answers are wrong

- In what state are bipolar transistor's junctions in saturation mode? 2a21.

- A. Emitter junction is close, collector open

- B. Emitter junction is open, collector close

- C. Both junctions are open D. Both junctions are close

- E. Saturation mode has no connection with the states of junctions

- 2a22. Why is not resistance applied as stable current source in differential amplifier?

- A. Large resistances, characteristic of current source, are not possible to realize in semiconductor ICs

- B. Large voltage drop is obtained on the resistance of large nominal, which leads to the increase of power supply voltage value

- C. The resistance cannot be current source at all

- D. A., B. answers are wrong

- E. All the answers are wrong

- What is the function of the output cascade of OpAmp? 2a23.

- A. Current amplifier

- B. Power amplifier

- C. Provides small output resistance

- D. B., C. answers are correct

- E. All the answers are wrong

- **2a24.** Why with bipolar transistors, minimum values of output signals of differential amplifier for small signal application are limited by approximately -0.7V level?

- A. Due to one of transistors falling into saturation mode

- B. Due to one of transistors collector opening

- C. Due to closing of one of transistors

- D. A., B. answers are correct

- E. Due to value limitation of collector resistance

- What should the structure of MOS transistor look like to reduce body effect? 2a25.

- A. Square of the bulk diffusion must be large

- B. Bulk diffusion must be rounded over transistor.

- C. Bulk diffusion must be as close to the transistor as possible

- D. A and C answers are correct

- E. B and C answers are correct

- What signals are the switching capacitances controlled by? 2a26. A. Overlap clock signals

- B. Clock signals

- C. Multi-level clock signals

- D. Non overlap clock signals

- E. Non clock signals

- 2a27. Which ADC is principally the fastest?

- A. Sigma-delta

- B. Dual slope integrating AC

- C. SAR

- D. Integrating

- E. Pipeline

- 2a28. How can the channel modulation effect of a MOS transistor be reduced?

- A. By decreasing bulk potential

- B. By decreasing transistor's L

- C. By decreasing transistor's W

- D. By increasing transistor's W

- E. By increasing transistor's L

- **2a29**. How much is the NMOS source follower output voltage, when the input transistor is in saturation mode?

- A. Equal to supply voltage

- B. Equal zero

- C. Larger than input voltage by threshold voltage of input transistor

- D. Smaller than input voltage by threshold voltage of input transistor

- E. Equal to input voltage

- 2a30. What is the advantage of using field transistor in the input of DiffAmp?

- A. Input capacitance decreases

- B. Input resistance increases

- C. Input offset error decreases

- D. Has no advantage

- E. A, B and C answers are correct

- 2a31. Which of the listed ADC contains DAC?

- A. SAR

- B. Flash

- C. Integrating

- D. Dual slope integrating

- E. All the answers are correct

- **2a32**. By what element is channel modulation of MOS transistor presented in a small signal model? *A. Controlled voltage source*

- B. Resistance

- C. Controlled current source

- D. Capacitor

- E. RC circuit

- 2a33. The effect of what errors reduces in Pipeline ADC's digital correction application

- A. Errors, which depends on Gain of OpAmp

- B. Errors which depends on Capacitor values scaling

- C. Comparators offset error

- D. Comparators sensitivity

- E. C and D answers are correct

- 2a34. Which of the mentioned DAC is not used in ICs?

- A. R-string DAC

- B. R-2R DAC

- C. Charge scaling DAC

- D. Current DAC

- E. All are used

- 2a35. What is the ICs life time conditioned by?

- A. Supply voltage value

- B. Migration

- C. Leakage power

- D. Maximum clock frequency of IC

- E. All the answers are correct

- 2a36. By what element is the body effect of a MOS transistor presented in a small signal model?

- A. Controlled voltage source

- B. Resistance

- C. Controlled current source

- D. Capacitor

- E. RC circuit

- 2a37. What is the minimum value of OpAmp's negative feedback limited by?

- A. Input resistance of OpAmp

- B. Amplifying coefficient of OpAmp

- C. Minimum value of OpAmp's output load resistance

- D. A=1 value

- E. Minimum value of OpAmp's input current

- 2a38. What is the reason of differential amplifier's debalance?

- A. Non similarity of diffpair (transistor)

- B. Accuracy of current source

- C. Loads non matching

- D. A and B answers are correct

- E. A and C answers are correct

- 2a39. How many comparators does 8 bit two-stage Flash ADC contain?

- A. 15

- B. 30

- C. 255

- D. 31

- E. 63

- **2a40**. How many comparators does the single-stage 8-bit Flash analog to digital converter have? *A. 31*

- B. 7

- C. 255

- D. 63

- E. 127

- 2a41. What is the main disadvantage of a SAR analog to digital converter?

- A. limited accuracy

- B. low performance

- C. A and B answers are correct

- D. A, B and E answers are correct

- E. thermal instability

- **2a42**. What the high performance of ADC is conditioned by? *A. high performance of input switches*

- B. output change rate of output operational amplifier

- C. converter's capacity

- D. A, B and C answers are correct

- E. A and B answers are correct

- **2a43**. Why are differential amplifiers applied only in case of high ohmic loads?

- A. because they have two outputs

- B. because the reduction of load resistance reduces the amplification coefficient of differential signal

- C. because the reduction of load resistance leads to amplification of common-mode signal

- D. B, C and D answers are correct

- E. B and C answers are correct

- 2a44. Why aren't differential amplifiers used as a standalone amplifiers?

- A. because of too high output resistance

- B. because can't work with low ohmic loads

- C. because amplifying of differential signal changes wuth laod resistance

- D. A, B and C answers are correct

- E. A and B answers are correct

- **2a45**. What is body affect in a small signal model of a MOS transistor presented by? *A. current controlled current source*

- B. voltage controlled voltage source

- C. voltage controlled current source

- D. resistance

- E. current controlled voltage source

- **2a46**. By what is channel length modulation in a small signal model of a MOS transistor presented? *A. current controlled current source*

- B. voltage source

- C. capacitor

- D. resistor

- E. current controlled voltage source

- 2a47. What is the body effect of a MOS transistor conditioned by?

- A. potentials' difference of source and drain

- B. potentials' difference of source and gate

- C. potentials' difference of drain and substrate

- D. potentials' difference of gate and substrate

- E. potentials' difference of source and substrate

- 2a48. What is the channel length modulation of a MOS transistor conditioned by?

- A. potentials' difference of source and drain

- B. potentials' difference of source and gate

- C. potentials' difference of drain and substrate

- D. potentials' difference of gate and substrate

- E. potentials' difference of source and substrate

2a49.

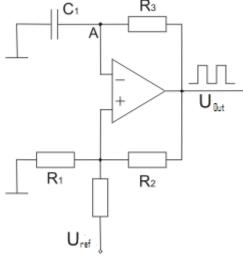

How will the change of R1 affect this generator?

- A. output amplitude will change

- B. output frequency will change

- C. amplitude at point A will change

- D. frequency at point A will change

- E. all the answers are wrong

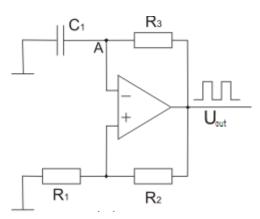

How will R1 change affect this generator? A. the amplitude of output pulses will change B. the frequency of output pulses will change C. the amplitude of A point pulses will change D. the frequency of A point pulses will change E. B, C and D answers are correct

The change of which element of this generator will lead to the change of frequency of output signal?

A. R<sub>2</sub>

*B*. *R*<sub>3</sub>

C. C<sub>1</sub>

D. B and C answers are correct

E. A, B and C answers are correct

2a52. Between which pins of a MOS transistor there is no direct capacitance?

- A. source and gate

- B. drain and gate

- C. gate and substrate

- D. source and substrate

- E. source and drain

- **2a53**. How can the conductance of a MOS transistor change in case of the given technology and gate source voltage? (ignore secondary effects)

A. changing gate drain voltage of a transistor

- B. changing drain source voltage of a transistor

- C. changing the sizes of channel

- D. not possible to change

- *E.* changing the sizes of source and drain

- 2a54. What does the MOS transistor in saturation mode represent?

- A. current source

- B. voltage source

- C. linear resistance

- D. resistance

- E. infinite small resistance

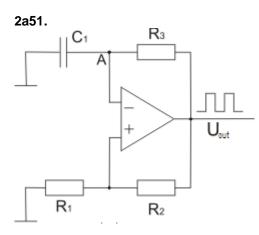

Within what limitations will U<sub>output</sub> voltage change when moving control of R<sub>1</sub> potentiometer form min position to max position

- A. from  $U_m$  to  $2U_m$

- B. from  $-U_m$  to  $-2U_m$

- C. from  $-2U_m$  to  $U_m$

- D. from  $-U_m$  to  $U_m$

- E. from  $-U_m$  to  $2U_m$

- **2a56**. What is the accuracy of digital-analog converter with R-2R matrix conditioned by? *A. accuracy of making matrix resistors*

- B. the value of voltage offset error of output OpAmp

- C. the gain of output OpAmp

- D. A and B answers are correct

- E. A, B and C answers are correct

- 2a57. How can amplifying coefficient of single stage common source resistive load amplifier be increased?

- A. increasing resistance value

- B. increasing channel width

- C. increasing channel length

- D. A and B answers are correct

- E. A and C answers are correct

# b) Problems

## 2b1.

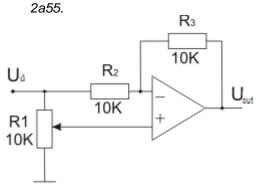

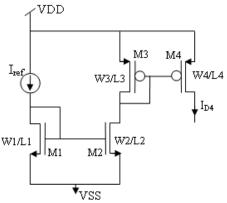

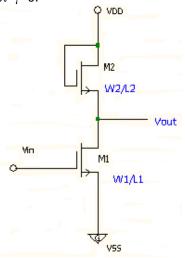

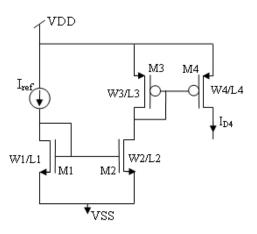

For the following circuit find  $I_{D4}=f(I_{ref})$  dependence if  $\lambda=0$ ,  $L_1=L_2=L_3=L_4$ ,  $W_1=W_2$ ,  $W_3=W_4$ . Consider all the transistors are in saturation mode.

# 2b2.

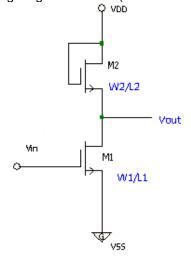

For the following circuit define small signal gain constant (assume M1 is saturated and  $\lambda$ =0,  $\gamma$ =0).

## 2b3.

For the following circuit define the value of input voltage in case of which M1 is out of saturation mode, if  $(W/L)_1=49 (W/L)_2=9 V_{TH}=0.7 VDD=3$ ,  $\lambda=\gamma=0$ .

# 2b4.

A current mirror is given by transistors' geometrical sizes. Find the gate voltage of M1 transistor.

## 2b5.

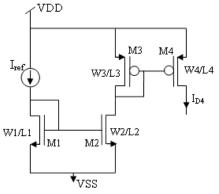

For the following circuit find the drain current of M4 transistor if all the transistors are in saturation. Ignore channel length modulation ( $\lambda$ =0).

# 2b6.

For the following circuit find V<sub>ref</sub>, if  $\mu_n$ =550 cm<sup>2</sup>/Vs,  $\epsilon_{Si02}$ =3.9,  $\epsilon_0$ =8.85\*10<sup>-14</sup> F/cm, t<sub>ox</sub>=0.16 nm, V<sub>thn</sub>=0.8V, V<sub>DD</sub>=2V, V<sub>SS</sub>=0V, W=L=10 um, \lambda=0, R=10 kOhm.

## 2b7.

For the following circuit define how much I<sub>out</sub> will change if V<sub>DD</sub> changes by  $\pm$  10% and if the transistor is in saturation and W=50um, L=0.5um, I<sub>out</sub>=0.5mA, K<sub>n</sub>=120 uA/V<sup>2</sup>, V<sub>TH</sub>=0.5V VDD=3V, (nominal value), R<sub>2</sub>/R<sub>1</sub>=0.35,  $\lambda$ =0.

#### 2b8.

Find the cutoff frequency of the following circuit and build amplitude-frequency characteristics, if  $R_1$ ,  $R_2$  and C are known.

2b9.

What does  $I_{out}$  equal when the transistor is in saturation (express transistor's conductivity by  $g_m$ ). Ignore body effect and channel modulation.

#### 2b10.

Find Vout depending on Vin, if the transistor is in saturation. Ignore body effect and channel modulation.

# 2b11.

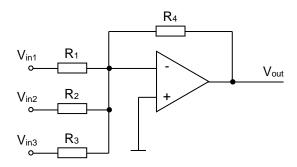

R1, R2, R3, R4 resistances are given. Find  $V_{out} = f(V_{in1}, V_{in2}, V_{in3})$ , considering the real K<sub>A</sub> amplifying coefficient.

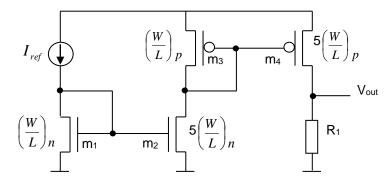

**2b12.**  $\left(\frac{W}{L}\right)_{n}$ ,  $\left(\frac{W}{L}\right)_{p}$ ,  $I_{ref}$ ,  $R_{1}$  values are given. Find  $V_{out}$ , ignore channel modulation.

#### 2b13.

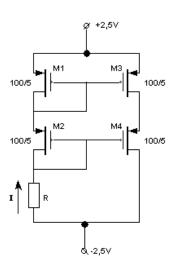

For the following circuit find the  $I_{D4}=f(I_{ref})$  dependence, if  $\lambda=0$ ,  $L_1=L_2=L_3=L_4$ ,  $W_1=W_2=3W_3=6W_4$ . All transistors are saturated.

## 2b14.

Calculate how much will lout change, if VDD increase by 10%: Given W, L,  $\mu$ n, V<sub>TH</sub>, C<sub>OX</sub>, R<sub>2</sub>, R<sub>1</sub>. Transistor is saturated, secondary effects can be neglected.

# **2b15.** Calculate the value of R, if M1 transistor is saturated and given are VDD, Vref, V<sub>TH</sub>, $\beta$ , R<sub>1</sub>, R<sub>2</sub>, $\lambda$ =0:

# **3. RF CIRCUITS**

# a) Test questions

- 3a1. Define super-heterodyne receiver's intermediate frequency if the input signal frequency is fs = 900 MHz, and heterodyne frequency is fh = 700 MHz

- A. 200 MHz

- *B. 600* MHz

- C. 1400 MHz D. 1600 MHz

- E. 1800 MHz

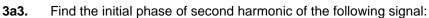

#### Which of the shown circuits is called "Inductive triple point"? 3a2.

E.

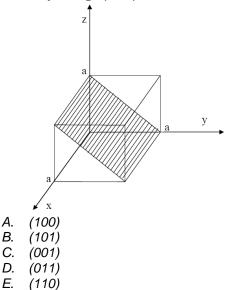

$$s(t) = \sum_{n=1}^{2} \frac{2}{n} \cos \left[ 2\pi n \cdot 10^{6} t + \frac{\pi}{n} (-1)^{n+1} \right]$$

А.  $-\pi$  $\frac{\pi}{2}$ В. 0 С.  $\frac{\pi}{2}$ D. E.  $\pi$

# 4. SEMICONDUCTOR PHYSICS AND ELECTRONIC DEVICES

## a) Test questions

- 4a1. Which circuit based on operational amplifier has transfer function with hysteresis?

- A. Non-inverting amplifier

- B. Inverting adder

- C. Comparator without feedback

- D. Comparator with positive feedback

- E. Comparator with negative feedback

## 4a2. Does semiconductor diode's I/V characteristics differ from I/V characteristics of ohmic resistance?

- A. Yes, it depends on the applied voltage direction and is nonlinear

- B. Yes, it depends on the applied voltage direction and is linear

- C. No, as the more direct voltage, the more is the current

- D. Partially, as current exists irrespective of voltage direction

- E. The correct answer is missing

- 4a3. What parameters of semiconductor material are needed for transistor fabrication?

- A. Charge carriers' mobility and concentration

- B. Charge carriers' concentration, minority charge carriers' life time, mobility

- C. Charge carriers' concentration and diffusion coefficient

- D. Charge carriers' concentration, diffusion coefficient, mobility, band gap

- E. The correct answer is missing

- **4a4.** Which regions does the graph of drain current dependence on source-drain voltage for p-n junction field effect transistor consist of?

- A. Linear dependence, saturation

- B. Linear dependence, saturation, breakdown

- C. Linear dependence, transition, saturation, breakdown

- D. Linear dependence, transition, breakdown

- E. The correct answer is missing.

- **4a5.** In what way are the oxide layer capacitor C<sub>0</sub>, the surface state capacitor C<sub>ss</sub> and the differential capacitor of the surface charge layer connected between each other in MOS structure?

- A. Css and  $C_0$  parallel, and with Csc sequentially

- B. Css and Csc parallel, and with C<sub>0</sub> sequentially

- C. C<sub>0</sub> and Csc sequentially, and with Csc parallel

- D. All capacitors are connected parallel to one another

- E. The correct answer is missing.

- **4a6.** How does differential resistance of p-n junction change parallel to direct current increase? *A. Does not change*

- B. Decreases

- C. Increases

- D. Increases, then decreases

- E. The correct answer is missing

- **4a7.** How many times will diffusion capacitance of bipolar transistor increase if its base length is increased twice?

- A. Will not change

- B. Will increase  $\sqrt{2}$  times

- C. Will increase 4 times

- D. Will decrease twice

- E. The correct answer is missing

- **4a8.** How does the p-n-p bipolar transistor's transfer factor depend on diffusion length of holes  $L_n$

- A. No dependence

B. Increase with increase of

$$L_p$$

by  $\beta = 1 - \frac{W}{2L_p}$  law

- C. Increase with increase of  $L_p$  by  $\beta = 1 \frac{1}{2} \left( \frac{W}{L_p} \right)^2$  law

- D. Decreases

- E. The correct answer is missing

- The light of what maximum wavelength can influence the current of silicon ( $E_g = 1.1 \text{ eV}$ ) 4a9. photodiode?

- A.  $\lambda_{max} = 1130 \text{ nm}$

- B.  $\lambda_{max} = 550 \text{ nm}$

- C.  $\lambda_{max} = 1240 \text{ nm}$

- D.  $\lambda_{max} = 335 \text{ nm}$

- E. The correct answer is missing

- How is bipolar transistor's current gain expressed in common base circuit with the help of emitter 4a10. effectiveness  $\gamma$ , transition coefficient  $\beta$  and collector's avalanche multiplication factor M?

A.

$$\alpha = \frac{\gamma \beta}{M}$$

B.  $\alpha = \gamma \beta M$

C.  $\alpha = \frac{M}{\gamma} \beta$

D.

$$\alpha = \frac{\beta}{\nu M}$$

- E. The correct answer is missing

- Is operating temperature range of ICs, computers and other semiconductor devices conditioned 4a11. by the used semiconductor material's band gap?

- A. Yes, the more the band gap, the more temperature range

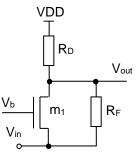

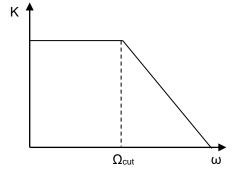

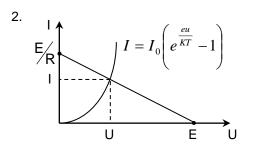

B. No, as concentration of minority charge carriers is independent from temperature